I2C User Guide

REVISION HISTORY¶

| Revision No. | Description |

Date |

|---|---|---|

| 1.0 | 04/09/2025 |

1. Overview¶

1.1 I2C¶

I2C, short for Inter-Integrated Circuit, is an integrated circuit bus that uses a multi-master to multi-slave architecture. It is a serial, synchronous, half-duplex communication bus that includes Serial Clock Line (SCL) and Serial Data Line (SDA), both of which are bidirectional IO lines. During communication, the clock signal is provided entirely by the master device; the data signal depends on whether the master device is performing a read or write operation. When performing a write operation, the data signal is provided by the master device. Conversely, when performing a read operation, the data signal is provided by the slave device.

1.2 MIIC¶

MIIC, or Master IIC Device, is an IP provided by SigmaStar specifically to act as the master device in I2C communications. It can communicate with various external I2C slave devices, meeting the needs of most devices that comply with the I2C communication protocol.

The relationship between device nodes and hardware groups is shown in the table below:

| MIIC Group | bank addr | DEV |

|---|---|---|

| HW MIIC group0 | 1114H | /dev/i2c-0 |

| HW MIIC group1 | 1115H | /dev/i2c-1 |

| HW MIIC group2 | 1116H | /dev/i2c-2 |

| HW MIIC group3 | 1117H | /dev/i2c-3 |

| HW MIIC group4 | 1118H | /dev/i2c-4 |

| HW MIIC group5 | 3EH | /dev/i2c-5 |

2. Key Words¶

dts/dtsi:

Linux Device Tree File, commonly used to describe the peripherals supported by the CPU. The attribute values contained in the peripheral nodes can be used for the configuration of the peripherals.

padmux:

Pin Multiplexing, used to connect the functional pins of a module to specific external pins, thereby establishing signal connections.

open-drain:

Open Drain Output, does not output voltage. When controlling the pin to output a low level, the pin is grounded; when controlling the pin to output a high level, it is in a high-impedance state, with the external circuit responsible for driving the high level.

push-pull:

Push-Pull Output, capable of outputting both low and high levels. It is typically composed of two transistors or MOSFETs with similar parameters, providing strong driving capability.

3. FUNCTION DESCRIPTION¶

3.1 Communication Protocol¶

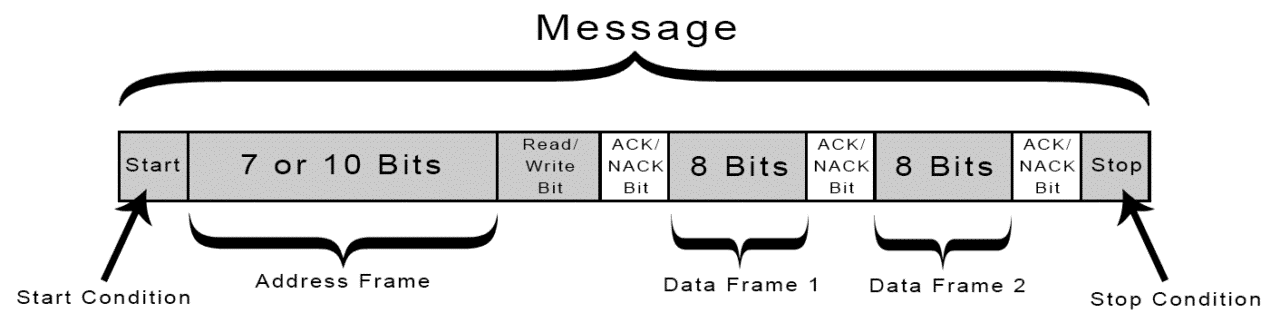

A complete I2C communication sequence must include: a Start Signal, Slave Device Address with Read/Write Bit, Acknowledge (ACK) Signal, data of arbitrary byte length, and a Stop Signal.

Start Signal: The first signal in an I2C communication sequence, generated by the master device. It indicates the beginning of communication. Electrical characteristics: SDA is pulled from high to low while SCL remains high.

Slave Device Address: Acts as the "unique identifier" for the slave device, sharing the address frame with the read/write bit. Occupies the upper 7 bits (for 7-bit addressing) or upper 10 bits (for 10-bit addressing). A slave device checks this address to determine if it is being addressed. Multiple devices with identical addresses on the same bus may cause communication failures or data corruption.

Read/Write Bit: Indicates whether the master is writing to or reading from the slave. Bit 0 (LSB) represents the operation:

0: Write operation;

1: Read operation

Example: For a 7-bit slave address 0x50 with a read operation:

address frame = (0x50 << 1) | 0x01 = 0xA1

Acknowledge (ACK) Signal: A feedback signal from the receiver (slave or master) to the sender. Low level (ACK) indicates successful reception; high level (NACK) indicates failure. During master-read operations, the master becomes the receiver after transmitting the slave address. Note: The clock (SCL) is always controlled by the master.

Data: Transmitted in byte units during read/write operations. For write operations, the slave address is typically followed by register addresses (8-bit or 16-bit), which are also treated as part of the data stream.

Stop Signal: The final signal in a communication sequence, generated by the master. It marks the end of communication. Electrical characteristics: SDA is pulled from low to high while SCL remains high.

I2C Communication Protocol Format as follow:

3.2 Function Configuration¶

Function |

Description |

Remark |

|---|---|---|

| FIFO transfer | Each transmission signal needs to be participated by the CPU, and different signals are sent by writing different MIIC registers | When using polling mode, the CPU loading will be relatively large; the maximum amount of data transmitted at a time is 8192 bytes; this mode is recommended when the amount of data transmitted each time is relatively small |

| DMA transfer | The entire communication process is operated by MIIC itself, and you only need to fill in the transmission content in advance and then trigger it; HW MIIC will communicate according to the timing settings that have been filled in | When using interrupt mode, the CPU loading will be smaller than FIFO mode; the maximum amount of data transmitted at a time is 4086 bytes; this mode is recommended when the amount of data transmitted each time is relatively large; when an error occurs during transmission, HW will immediately stop the communication and trigger an interrupt |

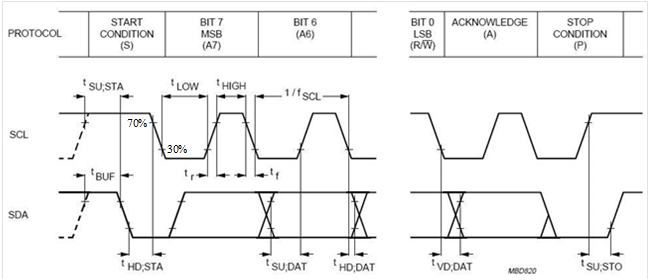

| Timing adjustment | Several I2C communication timings are available for adjustment. When a specific part of the timing does not meet the requirements of the slave device, adjust it in the dtsi node | Adjustable timing: t-SU-STA, t-HD-STA, t-SU-STO, t-HD-STO, t-SU-DAT, t-HD-DAT |

| Rate | Supports adjustable communication rate range, no gear classification, and can be adjusted in the dtsi node according to actual needs | Supports 50kHz - 1500KHz, and the higher rate requirement is not guaranteed |

| Output mode adjustment | Supports open-drain and push-pull output modes, which can be adjusted in the dtsi node | MIIC does not support arbitrary adjustment of the rising/falling edge time of the waveform, which can only be changed by adjusting the output mode, and the time cannot be confirmed. The push-pull rising edge time will be faster |

| Padmux | Different padmux can be configured to lead the bus to different pins | |

| 1toN | Some padmux will connect several groups of PAD pins at the same time, and the signal will be provided to these groups of PADs at the same time during communication | This method has the following limitations: All slave devices must be of the same type and address, and MIIC can only write data but not read data. It is generally used to connect to several identical slave devices at the same time and need to be set synchronously. |

| External pull-up | External pull-up must be connected to the I2C bus |

I2C Communication Timing as follow:

MIIC supports the following configurable timing parameters:

| Timing | Description |

|---|---|

| t-SU-STA | Start signal setup time |

| t-HD-STA | Start signal hold time |

| t-SU-STO | Stop signal setup time |

| t-HD-STO | Stop signal hold time |

| t-LOW | Clock low period |

| t-HIGH | Clock high period |

| t-SU-DAT | Data signal setup time |

| t-HD-DAT | Data signal hold time |

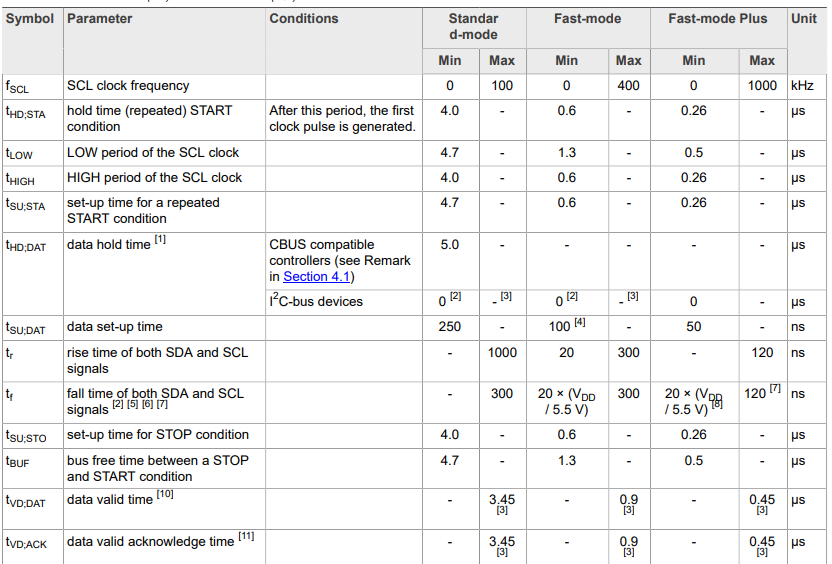

I2C divides communication speeds into multiple modes based on intervals:

| Speed Mode | Description |

|---|---|

| Standard-mode (Sm) | Up to 100k bit/s maximum |

| Fast-mode (Fm) | Up to 400k bit/s maximum |

| Fast-mode Plus (Fm+) | Up to 1M bit/s maximum |

| High-speed mode (Hs-mode) | Up to 3.4M bit/s maximum |

| Ultra Fast-mode (UFm) | Up to 5M bit/s maximum |

Timing Requirements for Sm/Fm/Fm+ Speed Modes as follow:

4. Introduction to Hardware Connections¶

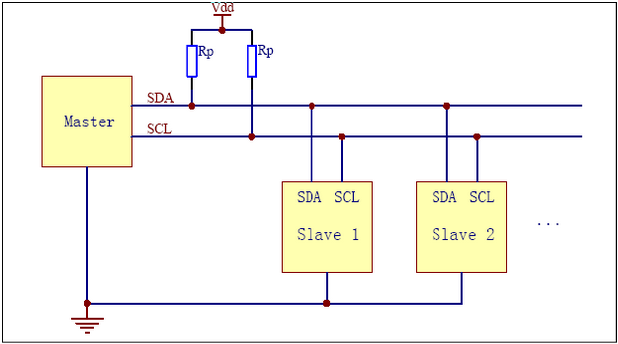

I2C follows a multi-master, multi-slave architecture. By definition, a single bus can host multiple master devices and multiple slave devices. Communication between devices is established through slave addresses and acknowledge (ACK) signals.

SigmaStar's I2C only provides one MIIC (master iic) master device on each bus, and there is no requirement for the number of slave devices, which can be set according to usage requirements.

In addition, in accordance with the I2C standard protocol, the external pull-up must be connected to the SDA and SCL of the bus. This is because I2C communication requires the ability to output a high level, and when the device output is an open-drain output, it cannot output a high level. At this time, the help of an external pull-up is needed to realize the "Wired-AND" function and determine the final level.

The following is an example diagram of the I2C bus:

5. UBoot Usage Instructions¶

5.1 UBoot Config¶

When compiling U-Boot, the configurations to be selected are as follows:

#menuconfig

Command line interface --->

Device access commands --->

[*] i2c

[*] SigmaStar drivers --->

[*] SigmaStar IIC

5.2. Dts configuration¶

I2C DTS Configuration only needs to configure the following information in the corresponding chipname.dtsi file.

i2c0: i2c0@1F222800 {

compatible = "sstar,i2c";

reg = <0x1F222800 0x200>;

clock-frequency = <200000>;

//dma-enable;

group = <0>;

//if u want set tSU/tHD, it should be set to a non-zero value, with units in ns

t-su-sta = <0>;

t-hd-sta = <0>;

t-su-sto = <0>;

t-hd-sto = <0>;

t-su-dat = <0>;

t-hd-dat = <0>;

//1->open drain; 2->open drain + one push; 3->open drain + mult push; 4->push-pull

output-mode = <2>;

status = "okay";

};

| Attrs | Description | Value | Note |

|---|---|---|---|

| compatible | Used to match the driver for registration, must be consistent with the code. | “sstar,i2c” | No modification required. |

| reg | Used to specify the address of the IIC register bank. | No modification required. | |

| clocks | Used to specify the clock source. | No modification required. | |

| group | Used to specify the IIC peripheral number or ID. | No modification required. | |

| speed | Used to select the IIC speed; directly enter the actual value. | eg. 250000 is 250K. | Can be modified as needed. |

| dma-en | Used to select whether to use DMA mode. | 1: Enable;;0: Disable | Can be modified as needed. |

| rd-ack-delay | Used to set the interval time before ACK | ns value | Can be modified as needed. |

| t-su-sta | Used to set the start signal setup time | ns value | Can be modified as needed. |

| t-hd-sta | Used to set the start signal hold time | ns value | Can be modified as needed. |

| t-su-sto | Used to set the stop signal setup time. | ns value | Can be modified as needed. |

| t-hd-sto | Used to set the stop signal hold time. | ns value | Can be modified as needed. |

| t-su-dat | Used to set the data signal setup time. | ns value | Must be less than tlow. When modifying this value and t-hd-dat, the modification of this value shall prevail. |

| t-hd-dat | Used to set the data signal hold time. | ns value | Must be less than tlow. When modifying this value and t-su-dat, the modification of t-su-dat shall prevail. |

| output-mode | Used to select the output method. | 1: Open-drain output; 2: Open-drain push 1T output; 3: Open-drain push multiple T strong pull-up; 4: Push-pull output; The rise time from 1 to 4 decreases sequentially. | |

| status | Used to select whether to enable the IIC master driver. | Can be modified as needed. |

5.3. U-Boot Command Parameters Explanation¶

-

Show current all I2C bus information and initialize the specified bus:

i2c bus <bus_num>

Paramter Name Description bus_num Enter 0~3 to select the I2C bus you want to initialize. If no input is provided, all available buses will be displayed -

Select I2C Bus

i2c dev <bus_num>

Paramter Name Description bus_num Enter 0~3 to select the I2C bus you want to use -

Scan Slave Devices

i2c probe <address>

Paramter Name Description address Test if a device with the address 'address' is connected. If not specified, it will scan all addresses from 0x00 to 0x7f -

Write Operation Command

i2c mw chip address[.0, .1, .2] value <count>

Paramter Name Description chip Slave Device Address address Register Address. Register Address Length (in bytes) value Write Data count Repeat Count -

Read Operation Command

i2c md chip address[.0, .1, .2] <length>

Paramter Name Description chip Slave Device Address address Register Address. Register Address Length (in bytes) length Number of Bytes to Read, default is 16 bytes if not specified

5.4. Uboot cmd Usage Example¶

i2c bus → i2c bus //List all buses

i2c dev → i2c dev 1 //specify I2C bus

i2c probe → i2c probe 0x50 //detect the slave with address 0x50

i2c mw → i2c mw 0x50 0x0000.2 0x12 0x1 //write 0x12 to slave 0x50

i2c md → i2c md 0x50 0x0000.2 0x01 //read 1 byte from slave 0x50

6. Kernel Usage Introduction¶

6.1. Kernel Config¶

When compiling the kernel, the configurations to be selected are as follows:

#menuconfig

Device Drivers --->

I2C support --->

<*> I2C device interface

Sstar SoC platform drivers --->

<*> Sstar I2C driver

6.2. Dts Configuration¶

You can set the basic parameters of the I2C driver by configuring the I2C entries in the dtsi. The dtsi parameters are displayed as follows:

i2c0: i2c@1f222800 {

compatible = "sstar,i2c";

reg = <0x0 0x1F222800 0x0 0x200>;

#address-cells = <1>;

#size-cells = <0>;

interrupts = <GIC_SPI INT_IRQ_MIIC IRQ_TYPE_LEVEL_HIGH>;

clocks = <&CLK_miic0>;

group = <0>;

dma-enable;

speed = <200000>;

//if u want set tSU/tHD, do not set 0, tSU = (t-su-* / i2c-srcclk)S, tHD = (t-hd-* / i2c-srcclk)S

t-su-sta = <0>;

t-hd-sta = <0>;

t-su-sto = <0>;

t-hd-sto = <0>;

t-su-dat = <0>;

t-hd-dat = <0>;

//1->open drain; 2->open drain + one push; 3->open drain + one push + clock push; 4->push-pull

output-mode = <2>;

status = "ok";

};

As shown above, the explanations for each parameter are as follows:

| Attribute | Description | Setting Value | Remark |

|---|---|---|---|

| compatible | Used to match the driver for driver registration. This attribute needs to be consistent with the code | “sstar,i2c” | Modification prohibited |

| reg | Used to specify the address of IIC register bank | No modification required | |

| interrupts | Used to specify the number and attribute of hardware interrupt | No modification required | |

| clocks | Used to specify the clock source in use | No modification required | |

| #address-cells | Used to specify the bit width of sub-node address | No modification required | |

| #size-cells | Used to specify the size of sub-node | No modification required | |

| group | Used to specify the number of IIC peripheral | No modification required | |

| speed | Used to select the IIC Speed, directly fill in the actual value | For example: 250000 means 250K | Can be modified if needed |

| dma-enable | Used to select whether to use DMA mode | Bool | Disable DMA function if not configured |

| t-su-sta | Used to set the start signal setup time | ns value | Can be modified if needed |

| t-hd-sta | Used to set the start signal hold time | ns value | Can be modified if needed |

| t-su-sto | Used to set the end signal setup time | ns value | Can be modified if needed |

| t-hd-sto | Used to set the end signal hold time | ns value | Can be modified if needed |

| t-su-dat | Used to set the data setup time | ns value | Can be modified if needed |

| t-hd-dat | Used to set the data hold time | ns value | Can be modified if needed |

| output-mode | Used to select the output mode | 1: open-drain output; 2: open-drain push 1T output; 3: open-drain push mult-T strong pull-up; 4: push-pull output | Can be modified if needed, 1->4 The rising edge time is shortened successively |

| status | Used to select whether to enable the IIC master driver | Can be modified if needed |

6.3. Padmux Configuration¶

The I2C padmux configuration method is consistent in both U-Boot and Kernel environments. You only need to add the following code in the corresponding padmux.dtsi based on the selected pins:

//I2C <PAD_GPIOE_00 PINMUX_FOR_I2C0_MODE_1 MDRV_PUSE_I2C0_SCL>, <PAD_GPIOE_01 PINMUX_FOR_I2C0_MODE_1 MDRV_PUSE_I2C0_SDA>, <PAD_GPIOE_04 PINMUX_FOR_I2C1_MODE_1 MDRV_PUSE_I2C1_SCL>, <PAD_GPIOE_05 PINMUX_FOR_I2C1_MODE_1 MDRV_PUSE_I2C1_SDA>, <PAD_GPIOE_21 PINMUX_FOR_I2C2_MODE_1 MDRV_PUSE_I2C2_SCL>, <PAD_GPIOE_22 PINMUX_FOR_I2C2_MODE_1 MDRV_PUSE_I2C2_SDA>, <PAD_GPIOE_23 PINMUX_FOR_I2C3_MODE_1 MDRV_PUSE_I2C3_SCL>, <PAD_GPIOE_24 PINMUX_FOR_I2C3_MODE_1 MDRV_PUSE_I2C3_SDA>, <PAD_GPIOD_01 PINMUX_FOR_I2C4_MODE_1 MDRV_PUSE_I2C4_SCL>, <PAD_GPIOD_02 PINMUX_FOR_I2C4_MODE_1 MDRV_PUSE_I2C4_SDA>, <PAD_PM_I2C_SDA PINMUX_FOR_PM_I2CM0_MODE_1 MDRV_PUSE_I2C5_SCL>, <PAD_PM_I2C_SDA PINMUX_FOR_PM_I2CM0_MODE_1 MDRV_PUSE_I2C5_SDA>,

As shown above, the first column is the pin index number, which can be found in /drivers/sstar/include/{chipname}/gpio.h;

the second column is the padmux value. In /drivers/sstar/include/{chipname}/padmux.h, the multiplexing relationship of all pins is listed. To check which multiplexing functions the pin supports, you can query the array;

the third column is the index number set for the padmux, which can be found in /drivers/sstar/include/mdrv_puse.h.

6.4. Module Usage Introduction¶

6.4.1. User-space Read and Write of I2C¶

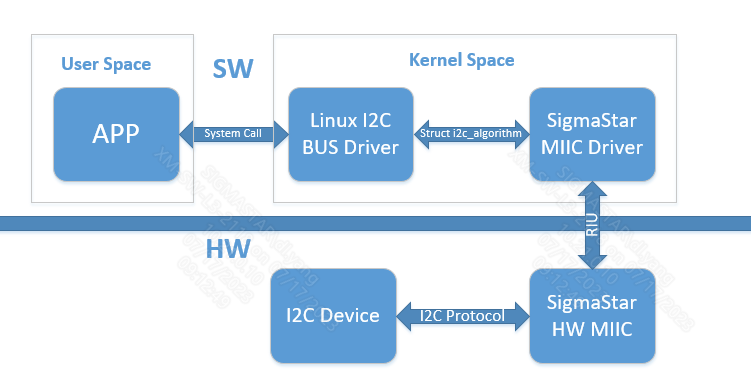

The overall kernel I2C call framework is shown in Figure 6-1. Starting from the user layer, the process involves opening the device node, obtaining the I2C's struct file_operations, and then invoking the ioctl system call. During this process, data is transferred between user space and kernel space. Execution proceeds to the SigmaStar I2C driver, which configures the hardware master device to enable communication with slave devices.

6.4.2 User-mode I2C Read/Write¶

Reading from and writing to I2C through standard system calls, usage examples can be referenced in:

kernel/drivers/sstar/i2c/ut/ut_i2cdev.c

The bit[1] of the flags variable is used to indicate whether a STOP signal is sent before a RESTART in I2C communication, meaning whether a STOP signal is sent after each i2c_msg transmission.

A single ioctl call can contain information for multiple struct i2c_message structures. For write operations, after each message is sent, you can choose whether to send a STOP signal, but the last message must send a STOP signal. For read operations, a STOP signal must be sent after each message.

For example, when we want to read data, we need to first write the register address from which we want to read. At this point, we can control whether to follow this write with a STOP signal by using bit[1] of the flags.

messages[0].flags = 0 // S+WR+RS+RD+P messages[0].flags |= 0x02 // S+WR+P+RS+RD+P

6.4.3. Kernel-mode I2C Read/Write¶

Operating I2C through standard kernel interfaces, the invocation method in kernel space can also issue multiple struct i2c_msg messages at once, just like in user space. It also allows you to choose whether each msg is followed by a STOP signal, similar to the description in user space, so it will not be repeated here.

struct i2c_adapter* adpa = NULL;

struct i2c_msg msg;

u8 data[4] = {0};

adpa = i2c_get_adapter(nr); //Get i2c-0 adapter

data[0] = reg & 0xff;

data[1] = value & 0xff;

msg.addr = slaveAddr>>1;

msg.flags = 0;

msg.buf = data;

msg.len = 2;

i2c_transfer(adpa, &msg, 1)

6.5. Sample code¶

Using the standard Linux I2C framework interface, the usage is as follows:

static int set_i2c_register(int bus, unsigned int addr, unsigned int reg, unsigned char *buf, unsigned int len) { struct i2c_rdwr_ioctl_data ioctl_packets; struct i2c_msg i2c_message[1]; char i2c_name[32]; unsigned char * write_buf; int i2c_file; int i; // open i2c dev node if (!snprintf(i2c_name, sizeof(i2c_name), "/dev/i2c-%d", bus)) { printf("set i2c name error\n"); exit(1); } if ((i2c_file = open(i2c_name, O_RDWR)) < 0) { printf("unable to open i2c control file"); exit(1); } write_buf = (unsigned char *)malloc(DOUBLE_BUF_DATA_LENGTH); i2c_message[0].addr = addr; i2c_message[0].flags = 0; i2c_message[0].len = len + 2; i2c_message[0].buf = write_buf; write_buf[0] = (reg >> 8) & 0x00ff; write_buf[1] = reg & 0x00ff; /* The first byte indicates which register we‘ll write */ /* * The second byte indicates the value to write. Note that for many * devices, we can write multiple, sequential registers at once by * simply making outbuf bigger. */ for (i = 0; i < len; i++) { write_buf[i + 2] = buf[i]; } /* Transfer the i2c packets to the kernel and verify it worked */ ioctl_packets.msgs = i2c_message; ioctl_packets.nmsgs = 1; do { if (ioctl(file, I2C_RDWR, &ioctl_packets) < 0) { free(write_buf); return 1; } } while (0); free(write_buf); return 0; }

7. API Reference¶

This functional module provides the following interfaces:

| API | Function |

|---|---|

| CamI2cOpen | Create device handle |

| CamI2cTransfers | Perform IIC transfer (synchronous) |

| CamI2cAsyncTransfer | Perform IIC transfer (Asynchronous) |

| CamI2cSetAsyncCb | Set IIC asynchronous transfer callback function |

| CamI2cWnWrite | Perform IIC transfer (synchronous with data splitting) |

| CamI2cWnAsyncWrite | Perform IIC transfer (Asynchronous with data splitting) |

To use these APIs, you need to include the header file drivers/sstar/include/cam_drv_i2c.h.

The data structures defined within it are as follows:

typedef struct i2cMsg { u16 addr; /* slave address */ u16 flags; #define I2C_M_RD 0x0001 /* read data, from slave to master */ /* I2C_M_RD is guaranteed to be 0x0001! */ #define I2C_M_TEN 0x0010 /* this is a ten bit chip address */ #define I2C_M_DMA_SAFE 0x0200 /* the buffer of this message is DMA safe */ /* makes only sense in kernelspace */ /* userspace buffers are copied anyway */ #define I2C_M_RECV_LEN 0x0400 /* length will be first received byte */ #define I2C_M_NO_RD_ACK 0x0800 /* if I2C_FUNC_PROTOCOL_MANGLING */ #define I2C_M_IGNORE_NAK 0x1000 /* if I2C_FUNC_PROTOCOL_MANGLING */ #define I2C_M_REV_DIR_ADDR 0x2000 /* if I2C_FUNC_PROTOCOL_MANGLING */ #define I2C_M_NOSTART 0x4000 /* if I2C_FUNC_NOSTART */ #define I2C_M_STOP 0x8000 /* if I2C_FUNC_PROTOCOL_MANGLING */ u16 len; /* msg length */ u8 *buf; /* pointer to msg data */ } tI2cMsg; typedef s32 (*sstar_i2c_async_calbck)(char para_msg_done, void *reserved); typedef struct { s32 nPortNum; void *pAdapter; } tI2cHandle;

7.1. CamI2cOpen¶

-

Function

Create device handle, return to pHandle

-

Declaration

s32 CamI2cOpen(tI2cHandle *pHandle, u8 nPortNum)

-

Parameters

Parameter Name Description pHandle Device Information nPortNum Bus Number -

Return Value

Return Value Description 0 Success other Failure

7.2. CamI2cTransfers¶

-

Function

Perform a single synchronous IIC transfer with the IIC channel corresponding to pHandle, using nMsgNum pMsg entries to store the transfer information.

-

Declaration

s32 CamI2cTransfer(tI2cHandle *pHandle, tI2cMsg *pMsg, u32 nMsgNum);

-

Parameters

Parameter Name Description pHandle Device Information pMsg Communication Content nMsgNum Information Length -

Return Value

Return Value Description Negative Failure other Success

7.3. CamI2cAsyncTransfer¶

-

Function

Perform a single asynchronous IIC transfer with the IIC channel corresponding to pHandle, using nMsgNum pMsg entries to store the transfer information.

-

Declaration

s32 CamI2cAsyncTransfer(tI2cHandle *pHandle, tI2cMsg *pMsg, u32 nMsgNum);

-

Parameters

Parameter Name Description pHandle Device Information pMsg Communication Content nMsgNum Information Length -

Return Value

Return Value Description 0 Success other Failure

7.4. CamI2cSetAsyncCb¶

-

Function

Set the callback function for IIC asynchronous transfer.

-

Declaration

s32 CamI2cSetAsyncCb(tI2cHandle *pHandle, sstar_i2c_async_calbck CalBck, void *pReserved);

-

Parameters

Parameter Name Description pHandle Device Information CalBck Callback Function Pointer pReserved Reserved Parameters -

Return Value

Return Value Description 0 Success other Failure

7.5. CamI2cWnWrite¶

-

Function

Perform a single synchronous IIC transfer with the IIC channel corresponding to pHandle, using nMsgNum pMsg entries to store the transfer information. After every WnLen bytes transferred, a delay of WaitCnt intervals is added.

-

Declaration

s32 CamI2cWnWrite(tI2cHandle *pHandle, tI2cMsg *pMsg, u32 nMsgNum, u32 WnLen, u16 WaitCnt);

-

Parameters

Parameter Name Description pHandle Device Information CalBck Callback Function Pointer pReserved Reserved Parameters WnLen Data will be split into several small blocks of WnLen bytes. WaitCnt After each small block is transferred, there will be a delay of wait_cnt counts -

Return Value

Return Value Description 0 Success other Failure

7.6. CamI2cWnAsyncWrite¶

-

Function

Perform a single synchronous IIC transfer with the IIC channel corresponding to pHandle, using nMsgNum pMsg entries to store the transfer information. After every WnLen bytes transferred, a delay of WaitCnt intervals is added.

-

Declaration

s32 CamI2cWnAsyncWrite(tI2cHandle *pHandle, tI2cMsg *pMsg, u32 nMsgNum, u32 WnLen, u16 WaitCnt);

-

Parameters

Parameter Name Description pHandle Device Information CalBck Callback Function Pointer pReserved Reserved Parameters WnLen Data will be split into several small blocks of WnLen bytes. WaitCnt After each small block is transferred, there will be a delay of wait_cnt counts -

Return Value

Return Value Description 0 Success other Failure

8. DEBUG¶

When communication abnormalities occur, you can refer to the following aspects for troubleshooting. Several common troubleshooting directions are provided. Additionally, it is recommended to capture waveforms during the debugging process for easier analysis.

| Troubleshooting Directions | Common Issues |

Note |

|---|---|---|

| External Pull-up | 1. Indicates a communication timeout error message; 2. Captured waveform shows no change, SCL remains low; 3. The data read and written in the captured waveform are all 0x00; | |

| padmux | 1. Indicates no ACK signal;2. The waveform shows no change, the level remains constant; | Refer to the PADMUX chapter, or the padmux module description; |

| Communication Rate | Communication failed, no ACK signal; | Check the slave device manual to confirm the normal operating communication rate range; |

| Clock Source | 1. Indicates a communication timeout error message;2. No waveform; | Refer to the CLKGEN module description; |

| Timing | Communication has no ACK signal; | If the slave device has specific requirements for detailed timing, check and confirm these from the device manual; |

| Slave Device Operating State | Communication has no ACK signal; | When the slave device is not in a normal working state, it cannot respond to signals initiated by the master device; |