Panel Configuration Reference

1. Basic Introduction¶

1.1 Overview¶

As the name suggests, screen parameters refer to the parameter configurations used by the screen. This document mainly explains the configuration of point screen, the meaning of screen parameters, and how to set the correct screen parameters.

1.2. Keyword Description¶

-

TTL/MIPI-DSI

TTL: Transistor-Transistor Logic, The interface signal is a digital signal that transmits parallel RGB data.

MIPI-DSI: Mobile Industry Processor Interface-Display Serial Interface, The interface signal is transmitted as a differential signal, transmitting RGB data, with high-speed HS and low-speed LP modes.

2. Introduction to screen parameter configuration files¶

2.1 Screen parameter configuration file path¶

project\board\$(chip)\$(boardname)\config\config_disp.json

2.2 Screen parameter configuration file composition¶

During the system startup process, the screen parameter configuration file will be parsed, and then different screen parameters will be saved in the system for use by the display module. The display module will obtain the required screen parameters from the system according to the parameter settings of the user calling the API. Please refer to the following for the process of obtaining screen parameters:MI_DISP_API

The composition of the screen parameter configuration file is shown in the following figure. mi_disp is the root node, which contains three child nodes: content, screen parameters and PQ.

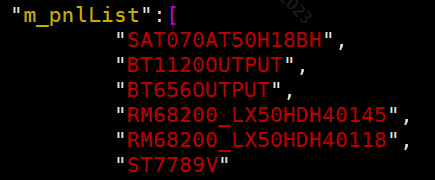

The content node is a collection of screen parameter name lists, which contains three child nodes: m_pnlList, m_btList, and m_mipidsiList.

-

m_pnlList

m_pnlList lists the screen parameter names of each interface type. User-defined screen parameters can be placed here, but one interface type can only correspond to one screen parameter. If the same type exists, only the first screen parameter will be selected.

-

m_btList/m_mipidsiList

m_btList lists the screen parameter names of BT656 with multiple resolutions, and m_mipidsiList lists the screen parameter names of mipidsi with multiple resolutions.

Screen parameters consist of section and variable name:

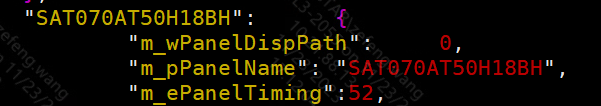

The section refers to the screen parameter name in the figure, EX: "SAT070AT50H18BH".

The variable name refers to the field on the left side of ":", and the right side is the value assigned to the variable name.

The section is unique and do not allow duplicate names, but variable names are allowed. As shown in the figure above, there can only be one section SAT070AT50H18BH, but m_pPanelName can be in different sections. The system distinguishes variable names according to different sections, and then adds different screen parameters.

3. Add screen parameters¶

-

The section name of the newly added screen parameter definition is not allowed to be the same as the existing section name

-

Newly added screen parameters can be placed in front of m_pnlList (only the first panel of the same type is valid). If there are screen parameters of the same interface type as the newly added screen parameters in m_pnlList, the original screen parameters of the same interface type can be deleted, or the newly added screen parameters can be added before the original interface screen parameters.

-

Add new screen parameters in the screen parameter node as shown below:

"SAT070AT50H18BH": { "m_wPanelDispPath": 0, "m_pPanelName": "SAT070AT50H18BH", "m_ePanelTiming": 52, "m_ePanelIntfType": 9, "m_wPanelHSyncWidth": 48, "m_wPanelHSyncBackPorch": 46, "m_wPanelVSyncWidth": 4, "m_wPanelVBackPorch": 23, "m_wPanelHStart": 98, "m_wPanelVStart": 27, "m_wPanelWidth": 1024, "m_wPanelHeight": 600, "m_wPanelHTotal": 1344, "m_wPanelVTotal": 635, "m_wPanelDCLK": 51000000, "m_bPanelInvDCLK": 0, "m_bPanelInvDE": 0, "m_bPanelInvHSync": 0, "m_bPanelInvVSync": 0, "m_wSpreadSpectrumFreq": 0, "m_wSpreadSpectrumRatio": 0, "m_ucPanelSwapChnR": 3, "m_ucPanelSwapChnG": 2, "m_ucPanelSwapChnB": 1, "m_ucPanelSwapRgbML": 0 },

4. Screen parameter description¶

4.1 Public Parameters¶

| Parameters | Description |

|---|---|

| m_pPanelName | panel name |

| m_ePanelTiming | Output resolution, 52 means user-defined |

| m_ePanelIntfType | Interface type BT656: 3 TTL: 9 MIPIDSI: 10 SRGB: 12 |

| m_wPanelHSyncWidth | Line synchronization signal pulse width |

| m_wPanelHSyncBackPorch | Horizontal synchronization signal back porch |

| m_wPanelVSyncWidth | Field sync signal pulse width |

| m_wPanelVBackPorch | Vertical sync signal back porch |

| m_wPanelHStart | m_wPanelHSyncWidth+m_wPanelHSyncBackPorch |

| m_wPanelVStart | m_wPanelVSyncWidth+m_wPanelVBackPorch |

| m_wPanelWidth | Number of effective pixels per row |

| m_wPanelHeight | Number of valid rows in the field |

| m_wPanelHTotal | m_wPanelWidth+m_wPanelHSyncWidth+m_wPanelHSyncBackPorch+HsyncFrontPorch |

| m_wPanelVTotal | m_wPanelHeight+m_wPanelVSyncWidth+m_wPanelVBackPorch+VsyncFrontPorch |

| m_wPanelDCLK | pixel clk: m_wPanelHTotal * m_wPanelVTotal * fps |

| m_bPanelInvDCLK | pixel clk polarity inversion |

| m_bPanelInvDE | DE polarity inversion |

| m_bPanelInvHSync | Hsync polarity inversion |

| m_bPanelInvVSync | Vsync polarity inversion |

| m_wSpreadSpectrumFreq | Clock stretch amplitude modulation (see SpreadSpectrumFreqCalculation for details) |

| m_wSpreadSpectrumRatio | Clock spread frequency modulation (see SpreadSpectrumFreqCalculation for details) |

| m_ucPanelSwapChnR | Swap channel R default = 0(Maintain the original connection of the physical circuit, that is, the R channel uses the corresponding signal source in the hardware design) 1: select R(Forcefully cover the channel signal source and replace the R-channel data with the R-channel signal output by the main control) 2: select G 3: select B |

| m_ucPanelSwapChnG | Swap channel G default = 0 1: select R 2: select G 3: select B |

| m_ucPanelSwapChnB | Swap channel B default = 0 1: select R 2: select G 3: select B |

| m_ucPanelSwapRgbML | Swap RGB MSB/LSB 0: disable M/L swap 1: enable M/L swap |

| m_ePanelRgbDataType | RGB data type or LCD data bus 0:E_MI_DISP_MHALPNL_RGB_DTYPE_RGB888, 1:E_MI_DISP_MHALPNL_RGB_DTYPE_RGB666, 2:E_MI_DISP_MHALPNL_RGB_DTYPE_RGB565, 3:E_MI_DISP_MHALPNL_RGB_DTYPE_RGB444, 4:E_MI_DISP_MHALPNL_RGB_DTYPE_RGB333, 5:E_MI_DISP_MHALPNL_RGB_DTYPE_RGB332, 6:E_MI_DISP_MHALPNL_RGB_DTYPE_BGR888, 7:E_MI_DISP_MHALPNL_RGB_DTYPE_BGR666, 8:E_MI_DISP_MHALPNL_RGB_DTYPE_BGR565, 9:E_MI_DISP_MHALPNL_RGB_DTYPE_BGR444, 10:E_MI_DISP_MHALPNL_RGB_DTYPE_BGR333, 11:E_MI_DISP_MHALPNL_RGB_DTYPE_BGR332, 12:E_MI_DISP_MHALPNL_RGB_DTYPE_YUV422_UY0VY1, 13:E_MI_DISP_MHALPNL_RGB_DTYPE_YUV422_VY0UY1, 14:E_MI_DISP_MHALPNL_RGB_DTYPE_YUV422_UY1VY0, 15:E_MI_DISP_MHALPNL_RGB_DTYPE_YUV422_VY1UY0, 16:E_MI_DISP_MHALPNL_RGB_DTYPE_YUV422_Y0UY1V, 17:E_MI_DISP_MHALPNL_RGB_DTYPE_YUV422_Y0VY1U, 18:E_MI_DISP_MHALPNL_RGB_DTYPE_YUV422_Y1UY0V, 19:E_MI_DISP_MHALPNL_RGB_DTYPE_YUV422_Y1VY0U |

| m_ePanelRgbDataSwap | RGB data swap, swap all data 0: disable 1: enable |

| m_wPadDrvngLvl | Adjust the pin driving capability. Set the driving capability level for all the pins of the interface. There are 4 levels in total 0: 4mA 1: 8mA 2: 12mA 3: 16mA |

Note: All m_ePanelRgbDataType are currently supported, with optional BT interfaces ranging from 12 to 19. Currently, m_wPadDrvngLvl only supports 0 and 1 files. m_ucPanelSwapRgbML is used to exchange the high and low bits of RGB data transmission, while m_ePanelRgbDataSwap is used to exchange all RGB data.

Schematic diagram of normal timing for m_bPanelInvDCLK, m_bPanelInvDE, m_bPanelInvHSync and m_bPanelInvVSync:

Schematic diagram of enabling polarity reversal timing for m_bPanelInvDCLK, m_bPanelInvDE, m_bPanelInvHSync and m_bPanelInvVSync:

4.2 MIPIDSI interface specific parameters¶

If it is a MIPI panel, MIPI DSI also needs to be configured.

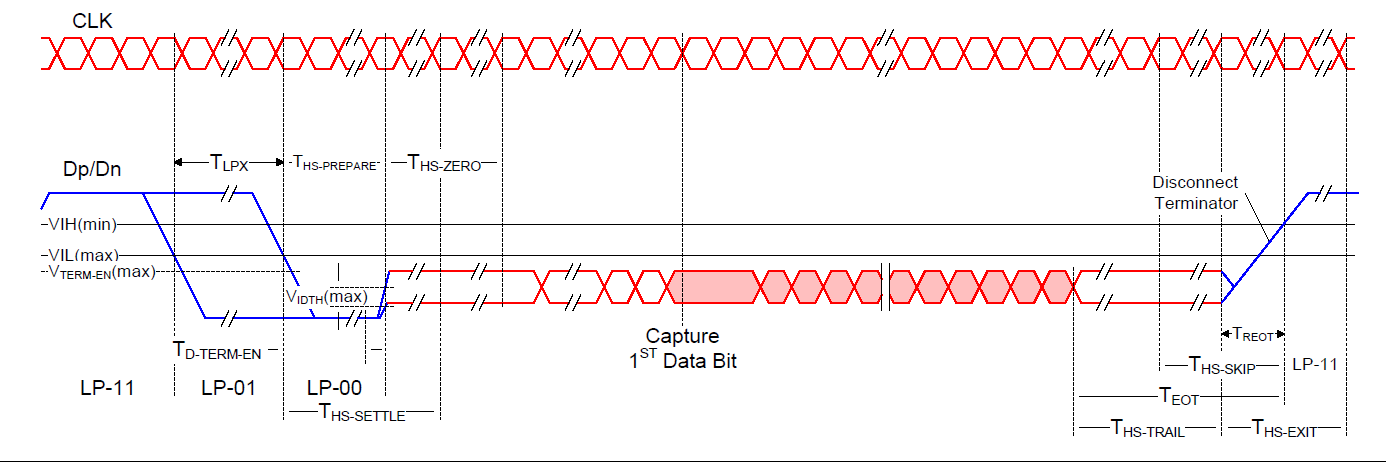

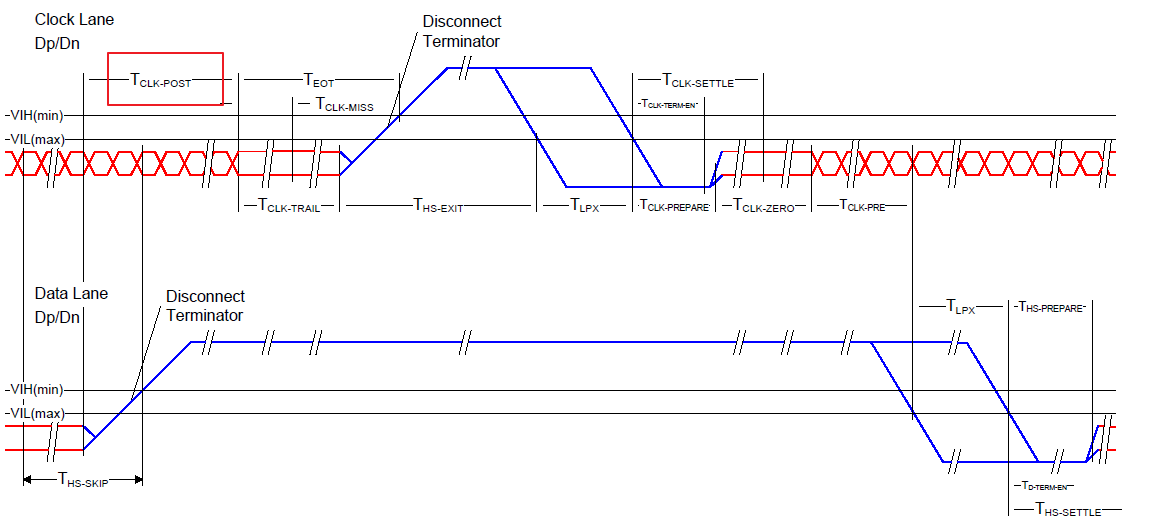

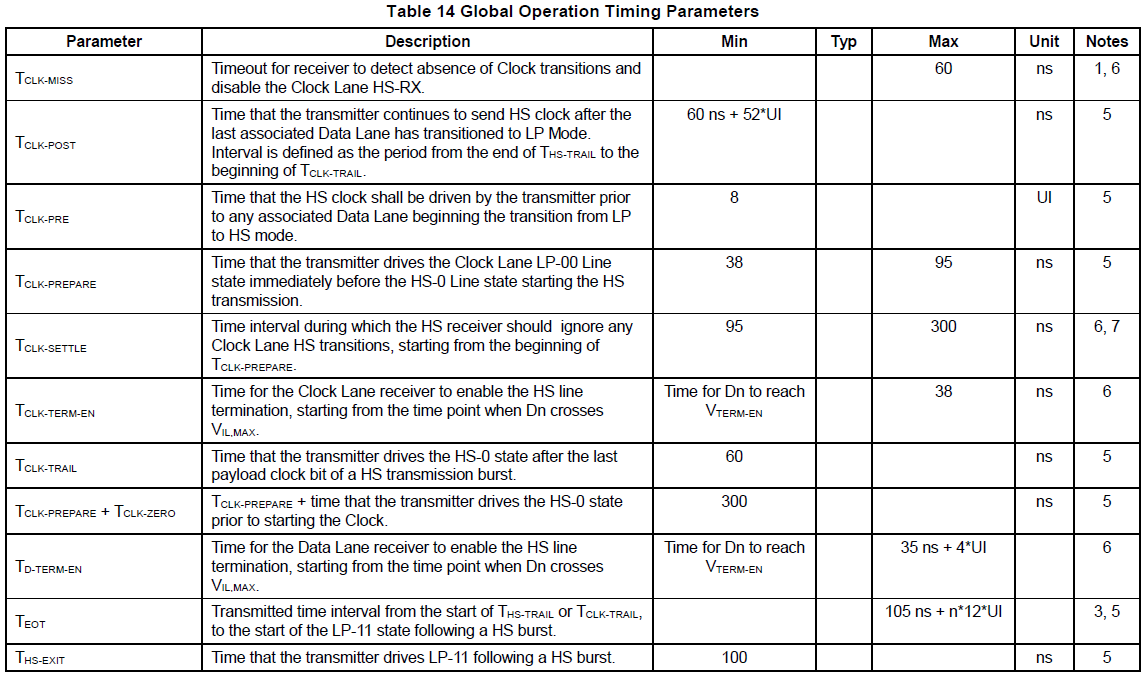

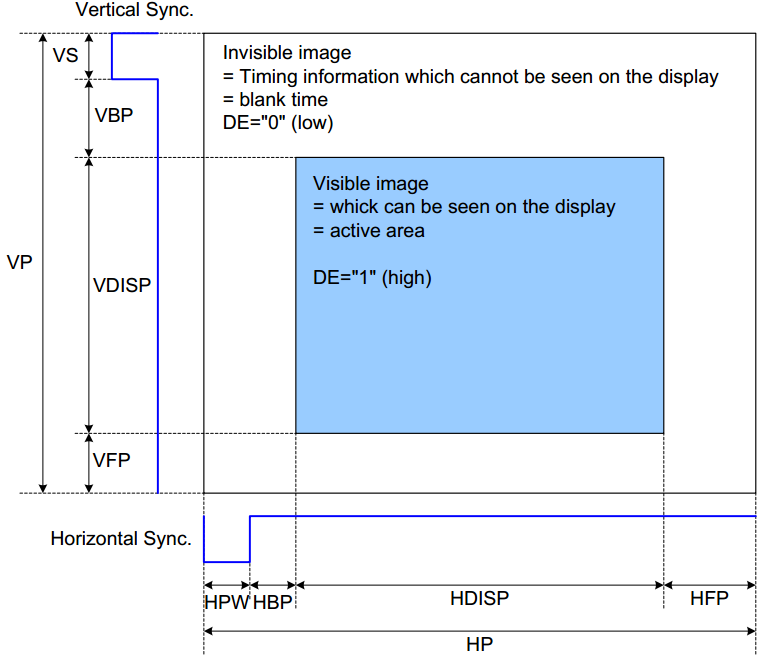

MIPI DSI parameter description:

Note: If there is no special timing requirement, the automatic calculation of m_wHsTrail, m_wHsPrpr, m_wHsZero, m_wDaHsExit, m_wClkTrail, m_wClkHsPrpr, m_wClkZero, m_wClkHsExit, m_wClkHsPost, m_wLpx, m_wTaGet, m_wTaSure, m_wTaGo, m_wContDet are supported. These parameters can be left blank and will be automatically calculated by the code.

Note: The above dphy parameters are sourced from MIPI_D-PHY_specification.pdf

| Parameters | Description |

|---|---|

| m_wHsTrail | T_{HS-TRAIL} (refer to the configuration file MIPIDSIParamCalculation) |

| m_wHsPrpr | T_{HS-PREPARE} (refer to the configuration file MIPIDSIParamCalculation) |

| m_wHsZero | T_{HS-ZERO} (refer to the configuration file MIPIDSIParamCalculation) |

| m_wDaHsExit | T_{HS-EXIT} (refer to the configuration file MIPIDSIParamCalculation) |

| Parameters | Description |

|---|---|

| m_wClkTrail | T_{CLK-TRAIL} (refer to the configuration file MIPIDSIParamCalculation) |

| m_wClkHsPrpr | T_{CLK-PREPARE} (refer to the configuration file MIPIDSIParamCalculation) |

| m_wClkZero | T_{CLK-ZERO} (refer to the configuration file MIPIDSIParamCalculation) |

| m_wClkHsExit | T_{HS-EXIT} (refer to the configuration file MIPIDSIParamCalculation) |

| m_wClkHsPost | T_{CLK-POST} (refer to the configuration file MIPIDSIParamCalculation) |

| Parameters | Description |

|---|---|

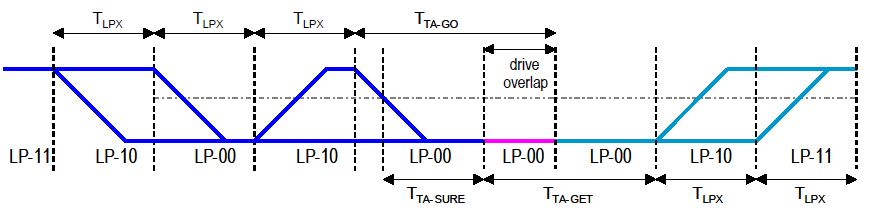

| m_wLpx | T_{LPX} (Reference file configurationMIPIDSIParamCalculation) |

| m_wTaGet | T_{TA-GET} (Reference file configurationMIPIDSIParamCalculation) |

| m_wTaSure | T_{TA-SURE} (Reference file configurationMIPIDSIParamCalculation) |

| m_wTaGo | T_{TA-GO} (Reference file configurationMIPIDSIParamCalculation) |

| m_wContDet | contention detection, default 0 (Reference file configurationMIPIDSIParamCalculation) |

| m_wBllp | blanking or low power interval, default 0 |

| m_wFps | frame per second, follow panel spec |

| m_eLaneNum | data lane number, 1 ~ 4 |

| m_eFormat | data output format 0: RGB565 1: RGB566 2: LOOSELY_RGB666 3: RGB888 |

| m_eCtrlMode | 0: CMD_MODE 1: SYNC_PULSE 2: SYNC_EVENT 3: BURST_MODE |

| m_wDataClkSkew | defult: 7 |

| m_ucPolCh0 | Channel 0 polarity 0: default 1:positive |

| m_ucPolCh1 | Channel 1 polarity 0: default 1:positive |

| m_ucPolCh2 | Channel 2 polarity 0: default 1:positive |

| m_ucPolCh3 | Channel 3 polarity 0:default 1:positive |

| m_ucPolCh4 | Channel 4 polarity 0:default 1:positive |

| m_ucClkLane | clk lane selection 0:select chn0 1:select chn1 2:select chn2 3:select chn3 4:select chn4 |

| m_ucDataLane0 | data lane0 selection 0:select chn0 1:select chn1 2:select chn2 3:select chn3 4:select chn4 |

| m_ucDataLane1 | data lane1 selection 0: select chn0 1: select chn1 2: select chn2 3: select chn3 4: select chn4 |

| m_ucDataLane2 | data lane2 selection 0: select chn0 1: select chn1 2: select chn2 3: select chn3 4: select chn4 |

| m_ucDataLane3 | data lane3 selection 0: select chn0 1: select chn1 2: select chn2 3: select chn3 4: select chn4 |

| m_pCmdBuff | MIPI panel cmd buffer, follow panel spec |

| m_pDeinitCmd | MIPI panel deinit cmd buffer, follow panel spec, content format is the same as m_pCmdBuff, delete this parameter if not needed |

m_pCmdBuff is the panel initialization cmd. This part is customized by each panel manufacturer according to the protocol annotation. Therefore, the setting content of this parameter is generally provided by the panel manufacturer. The setting content format of this parameter is as follows, filled in hexadecimal.

"m_pCmdBuff":[

"cmd1","data_num","data[0]","data[1]",...,"data[num-1]",

...,

"cmdN","data_num","data[0]","data[1]",...,"data[num-1]",

"0xFF","0xFF" //Terminator

]

| Parameters | Description |

|---|---|

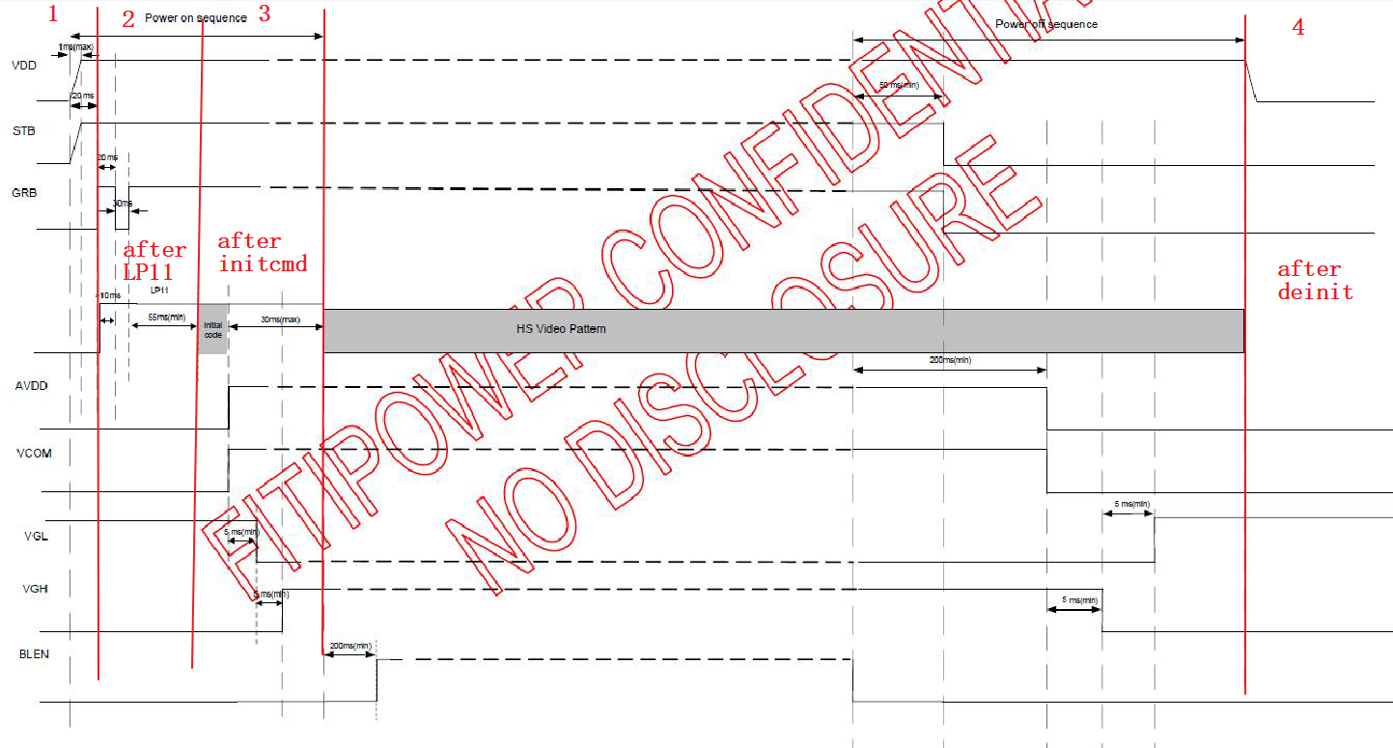

| m_pAfterLP11 | After LP11, power on timing control, delete this parameter if not needed |

| m_pAfterInit | After mipidsi init cmd is sent, power on timing control, if not needed, delete this parameter |

| m_pAfterDeinitCmd | After mipidsi deinit cmd is sent, power off timing control, if not needed, delete this parameter |

m_pAfterLP11, m_pAfterInit, and m_pAfterDeinitCmd are used to control the power-on and power-off timing of the screen. The content format is as follows. pin_idx must be followed by level and delay_ms, which are filled in decimal.

"m_pAfterLP11":[

"pin_idx","level","delay_ms",

"pin_idx","level","delay_ms",

...,

"pin_idx","level","delay_ms"

]

Example: seq-after lp11: Pull up gpio_179 and delay for 10ms ->Pull down gpio_179 and delay for 10ms ->Pull up gpio_179 and delay for 10ms

seq-after-lp11 = <179 1 10 179 0 10 179 1 10>; seq-after-initmd = <179 1 10 179 0 10 179 1 10>; seq-after-deinitcmd = <179 1 10 179 0 10 179 1 10>;

5. Configure the correct screen parameters¶

To configure the correct screen parameters, in addition to referring to the attached table in the above list, you also need to adjust the corresponding parameters according to the screen specification or protocol specification.

5.1 Screen Specifications¶

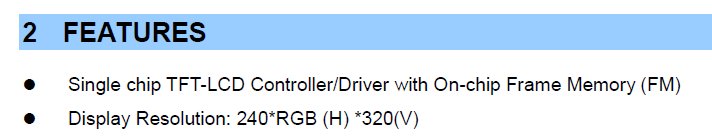

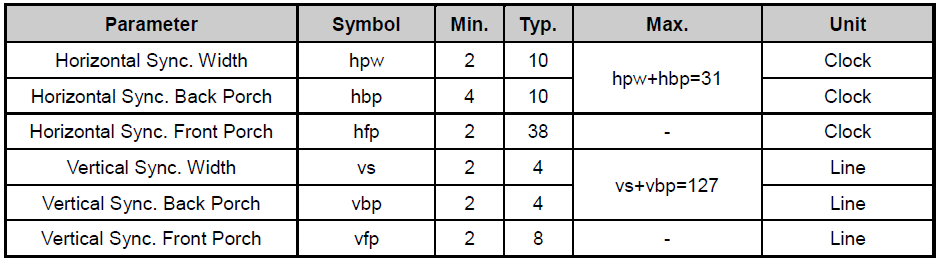

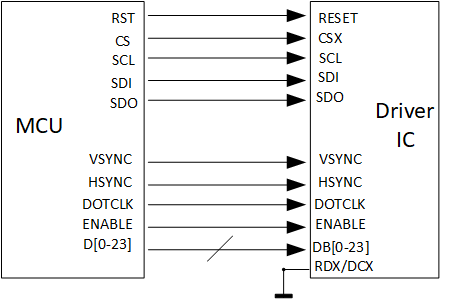

The Timing section can be found in the specification sheets of most screen chips, as shown in the figure below. If you can’t find it, you can ask the manufacturer.

| Parameters | Description |

|---|---|

| m_wPanelVSyncWidth | Horizontal Sync. Width |

| m_wPanelHSyncBackPorch | Horizontal Sync. Back Porch |

| m_wPanelVSyncWidth | Vertical Sync. Width |

| m_wPanelVBackPorch | Vertical Sync. Back Porch |

| m_wPanelHStart | m_wPanelHSyncWidth+m_wPanelHSyncBackPorch |

| m_wPanelVStart | m_wPanelVSyncWidth+m_wPanelVBackPorch |

| m_wPanelWidth | 240(H) |

| m_wPanelHeight | 320(V) |

| m_wPanelHTotal | m_wPanelHStart+m_wPanelWidth + hfp |

| m_wPanelVTotal | m_wPanelVStart+m_wPanelHeight + vfp |

5.2 Protocol Specification¶

If it is a MIPI panel, you also need to configure MIPI dphy related parameters according to the MIPI spec.

UI features: H_Total = m_wPanelHTotal V_Total = m_wPanelVTotal BitsPerPixel=24(RGB888)/18(RGB666)/16(RGB565) Bitrate = H_Total * V_Total * FPS * BitsPerPixel / lane number UI = 1/Bitrate

For example, the HS-PREPARE requirement in the table is greater than (40ns + 4 * UI) and less than (85ns + 6 * UI), then the corresponding parameters in MIPI dphy timing are

(40ns + 4 * UI) / 8 * UI < m_wHsTrail < (85ns + 6 * UI) / 8 * UI

The calculation methods for other MIPI dphy timing parameters are the same as above.

HPW, HBP, HFP must satisfy the following formula

data_init_cycle = HsExit + Lpx + HsPrpr + HsZero HFP_WC = HFP * BPP – 12 – data_init_cycle * lane_num HBP_WC = HBP * BPP – 10 HSA_WC = HPW * BPP – 10 HFP_WC/HBP_WC/HSA_WC need > 0

The above parameter calculations can refer to the document MIPIDSIParamCalculation.

6. TTL Configuration¶

6.1 Basic Concepts¶

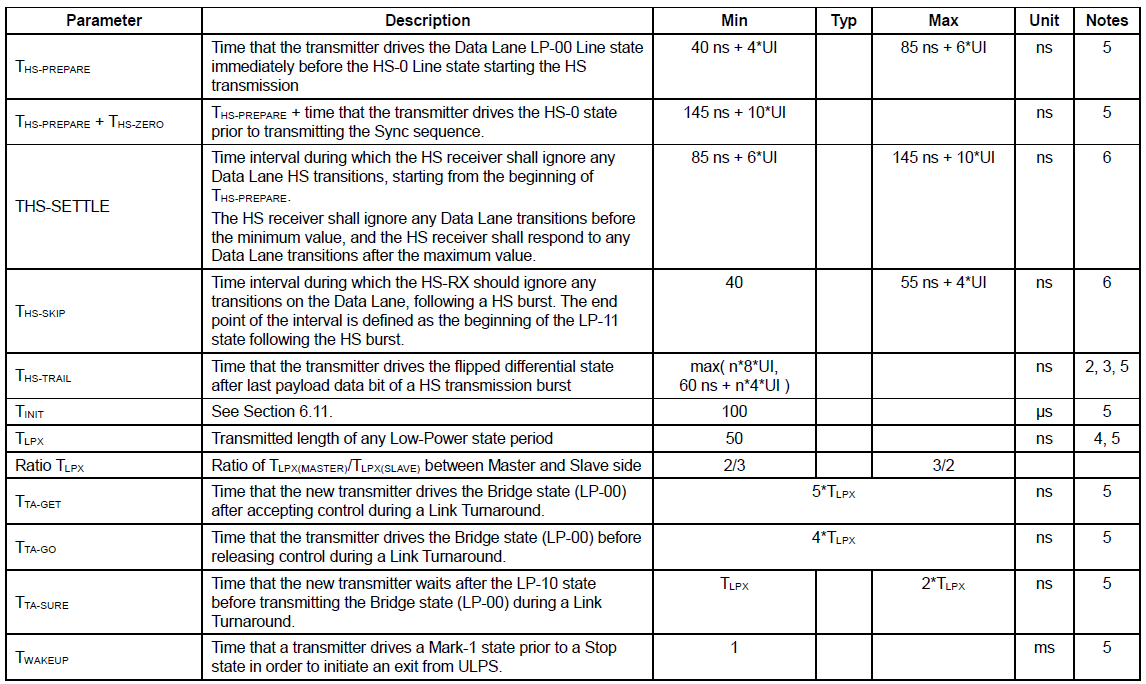

There are two types of Parallel RGB Interface, DE mode and HV mode. When DE is enabled, VSYNC, HSYNC, DOTCLK, DE, D[0-23] pins will be used. When HV mode is enabled, VSYNC, HSYNC, DOTCLK, D[0-23] pins will be used. Now the program uses DE mode by default. Please configure the relevant parameters according to DE mode.

Some panel driver ICs need to be initialized, that is, their internal registers need to be set. They usually communicate through SPI or IIC interfaces. The cmd and data required for initialization are provided by the panel manufacturer. The data format when sending needs to refer to the panel datasheet.

The Parallel RGB Interface panel uses HSYNC, VSYNC, DOTCLK, and DE as synchronization signals. RGB data is only displayed in the valid timing interval, and the blanking interval is an invisible area.

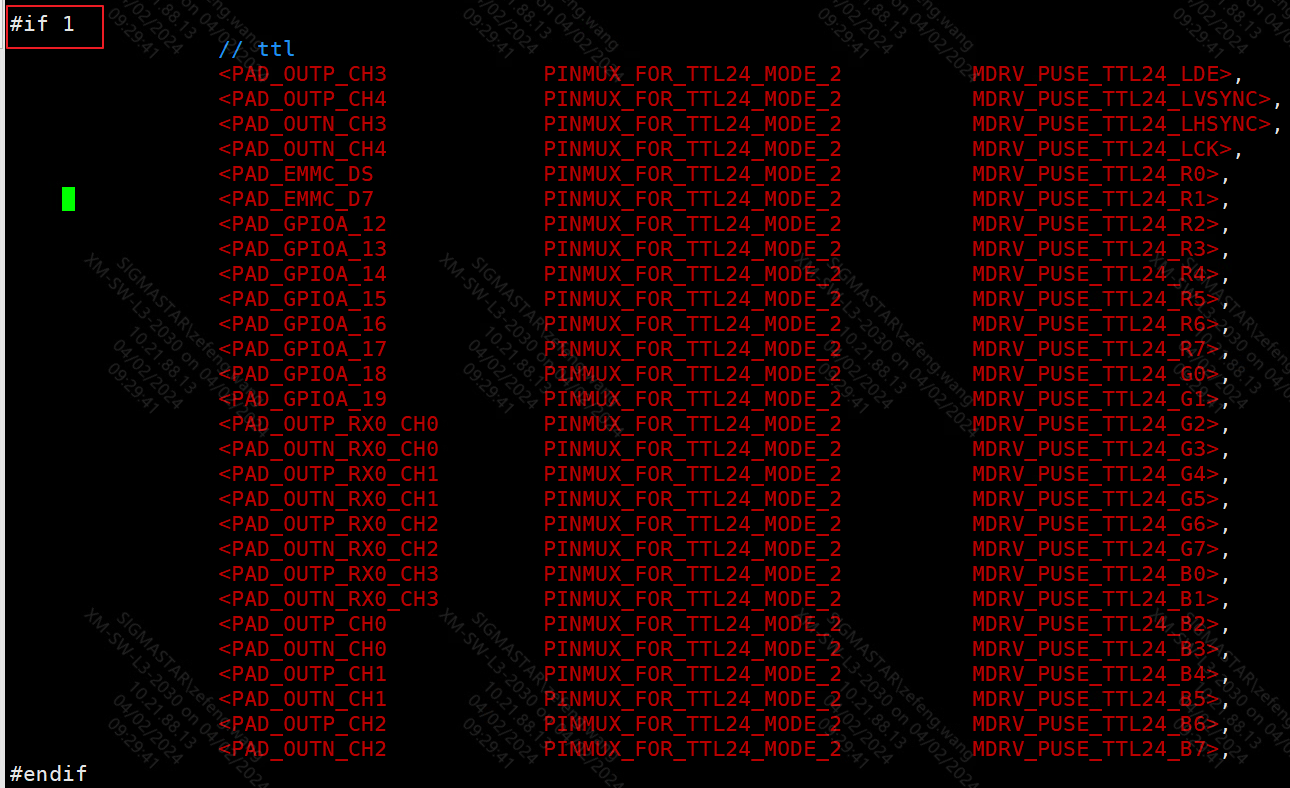

6.2 padmux¶

kernel/arch/arm64/boot/dts/sstar/$(boardname)-padmux.dtsi

You can configure it as follows, changing #if 0 to #if 1

6.3 Screen parameter configuration¶

For new screen parameter settings, please refer to Chapter 2. For screen parameter content settings, please refer to Chapters 4 and 5.

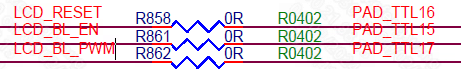

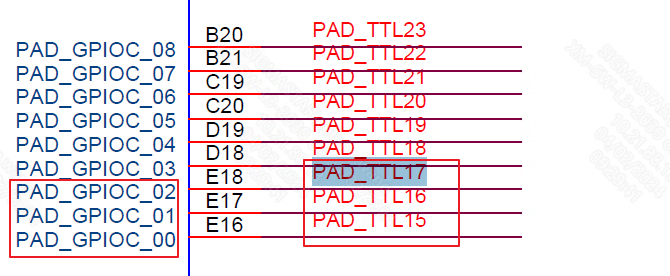

6.4 Backlight¶

If backlight control is required, first find the corresponding pin and the corresponding pad of the chip in the principle, and control the backlight by controlling the above pins.

7.MIPIDSI Configuration¶

7.1 MIPIDSI Specification¶

- 1-4 data lanes, 1 clock lane

- Level:

- LP: 0~1.2V

- HS: 100~300mV

- HS: 80Mbps ~ 2.5Gbps/lane

- Pixel format:

- 16 bpp (5,6,5 RGB) each pixel using two bytes

- 18 bpp (6,6,6 RGB) packed

- 18 bpp (6, 6, 6 RGB) loosely packed into three bytes

- 24 bpp (8, 8, 8 RGB), each pixel using three bytes

- video mode: BURST_MODE/SYNC_EVENT/SYNC_PULSE

- data chn swap

- data/clk chn P/N swap

- max resolution 2560x1440@60

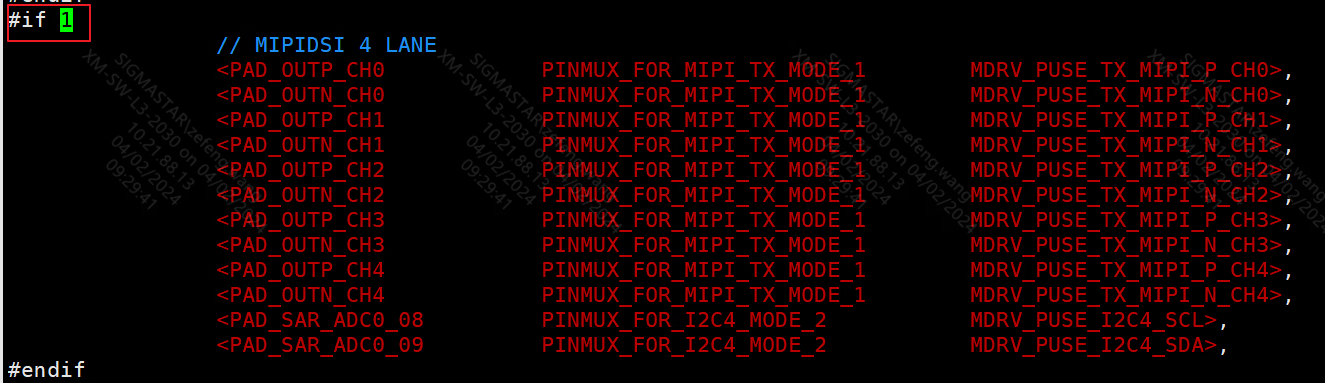

7.2 padmux¶

kernel/arch/arm64/boot/dts/sstar/$(boardname)-padmux.dtsi

You can configure it as follows, changing #if 0 to #if 1

7.3 Screen parameter configuration¶

For new screen parameter settings, please refer to Chapter 2. For screen parameter content settings, please refer to Chapters 4 and 5.

7.4 Backlight¶

Backlight control is consistent with TTL.