TIMER_DebugSop

REVISION HISTORY¶

| Revision No. | Description |

Date |

|---|---|---|

| 1.0 | 12/10/2024 |

1. Issue 1: The interrupt handler registered for the PM timer on the Linux side is not executed¶

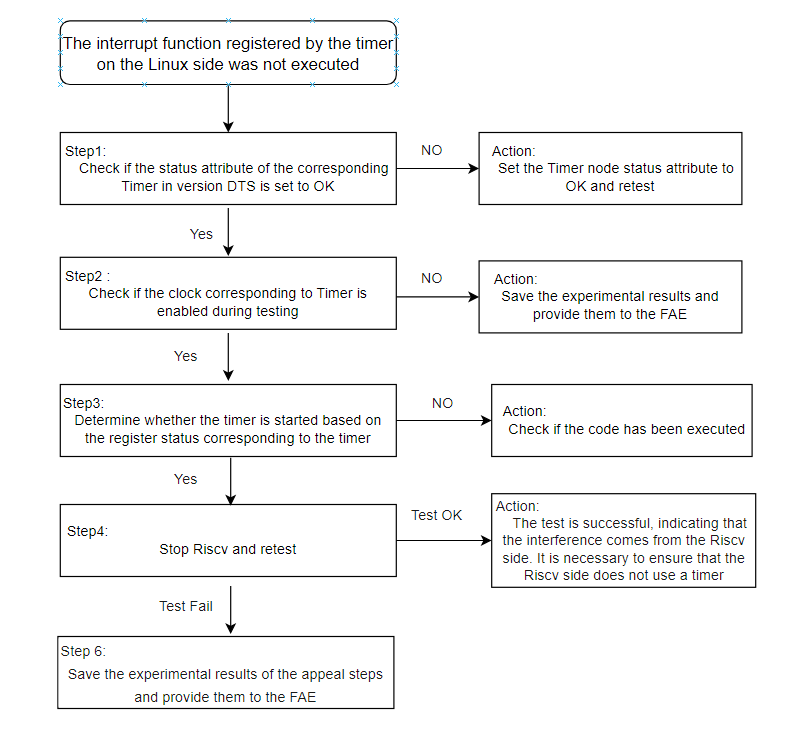

1.1 Debug Flowchart¶

1.2 Check if the Status attribute of the Timer node in the DTS is set to OK¶

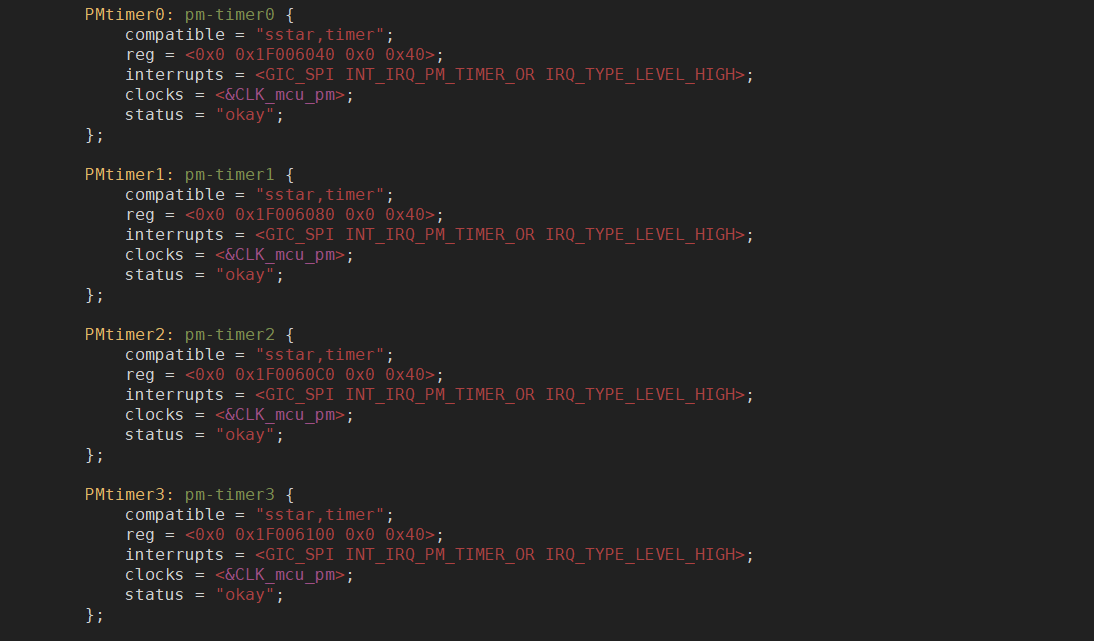

Currently, the default PM timer is used in RISC-V, and the NO-PM timer is used on the Linux side. If users need to use the PM timer on the Linux side, it is recommended not to use the PM timer on the RISC-V side.

1.3 Check if the clock corresponding to the PM timer is enabled¶

The difference between the PM timer on the PCUPID platform and other SOC PM timers is that the clocks for PM timers 4-7 are controlled separately. When using PM timers 4-7, it is necessary to ensure that their corresponding clocks are enabled.

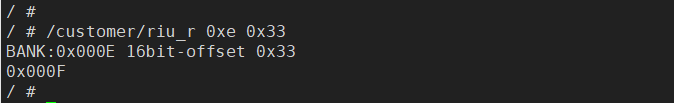

The 0-3 bits of register bank 0xe offset 0x33 control PM timers 4-7 sequentially, and the results can be obtained through /customer/riu_r 0xe 0x33. Normally, the clock is enabled by default after the system starts. If the clock is found to be disabled, it is recommended to seek assistance from FAE directly.

1.4 Check the corresponding registers of the PM Timer during operation¶

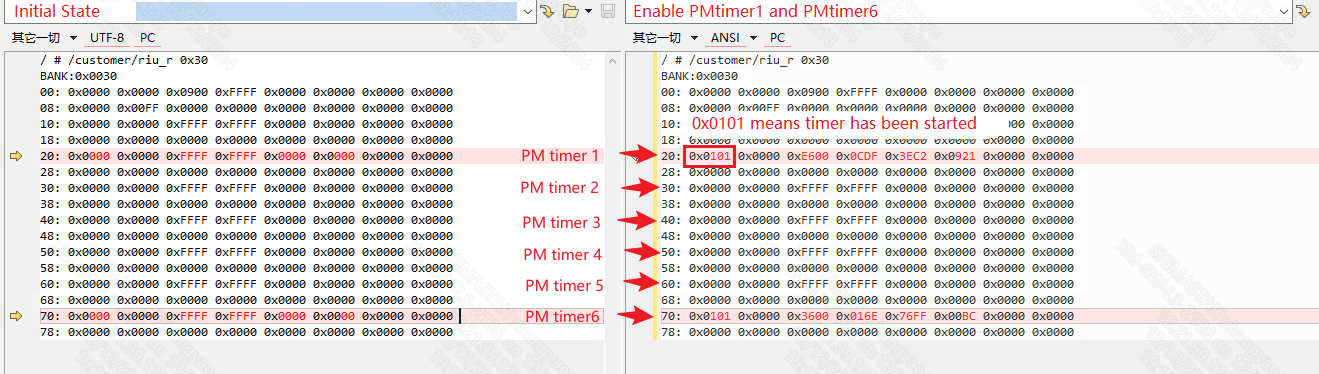

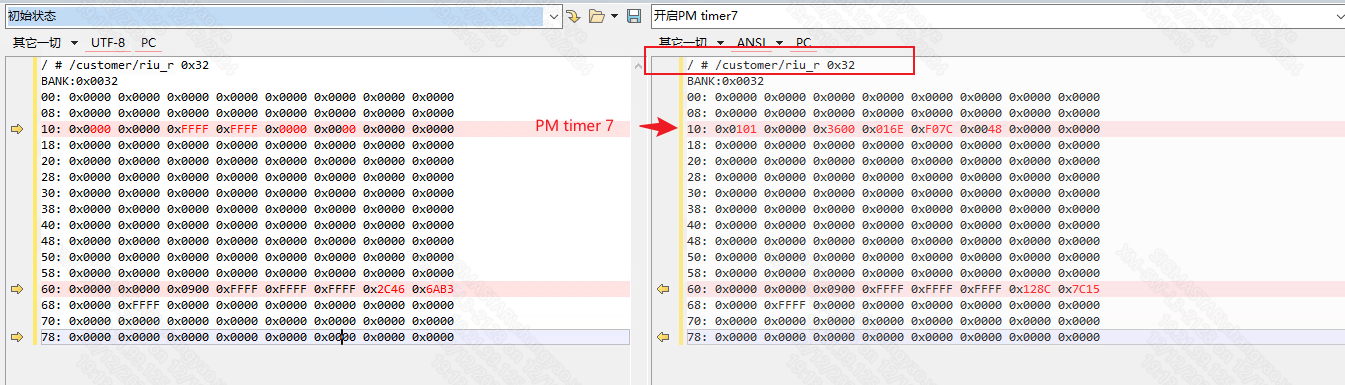

Users can determine the current state of the PM timer by checking the values of the corresponding registers. There are several registers involved with each PM timer; we will not delve into the significance of each register here, as our core goal is to determine whether the PM timer is functioning. As shown in the figure below, if the first register corresponding to the PM timer is 0x101, it indicates that the PM timer has been started.

It should be noted that the register address for PM timer 7 is in bank 0x32, as shown in the figure below.

1.5 Disable RISC-V and retest¶

If no issues are found through the above checks, it is recommended to disable RISC-V and retest. The command to disable RISC-V is:

echo 2 > /sys/class/sstar/riscv/reset

The Timer interrupt is reported to both RISC-V and Linux simultaneously. Sometimes, the interrupt function registered for the Timer on the Linux side may not be executed, likely due to interference from RISC-V. Disabling RISC-V and retesting can help eliminate this interference.

1.6 Seek assistance from FAE¶

When seeking assistance from FAE, please provide the results of the above steps.

2. Issue 2: The interrupt handler registered for the PM timer on the RISC-V side is not executed¶

The debugging approach for the issue of the PM timer interrupt handler not being executed on the RISC-V side is similar to that of the PM timer interrupt handler not being executed on the Linux side.

2.2 Check if the Status attribute of the Timer node in the DTS is set to disable¶

Currently, the default PM timer is used in RISC-V, and the NO-PM timer is used on the Linux side. If users need to use the PM timer on the RISC-V side, it is recommended not to use the PM timer on the Linux side.

2.3 Check if the clock corresponding to the PM timer is enabled¶

Refer to 1.3 Check if the clock corresponding to the PM timer is enabled.

2.4 Check the corresponding registers of the PM Timer during operation¶

Refer to 1.4 Check the corresponding registers of the PM Timer during operation.

2.5 ARM side only boots to uboot stage and retest¶

In the PCUPID platform solution, the ARM side uboot does not use the PM timer, which can eliminate interference from the ARM side on the use of the PM timer on the RISC-V side.

2.6 Seek assistance from FAE¶

When seeking assistance from FAE, please provide the results of the above steps.