RTC_DebugSop

REVISION HISTORY¶

| Revision No. | Description |

Date |

|---|---|---|

| 1.0 | 12/19/2024 | |

| 1.1 | 03/11/2025 |

Preface¶

This document aims to guide customers on how to conduct preliminary troubleshooting and identify some basic issues when encountering RTC-related problems during the development process.

1. Common Basic Operations and Commands for Debugging¶

1.1 echo Command¶

Supports obtaining hardware clock, system time, and other operations through the echo command. For details, see "RTC Usage Reference."

1.2 Common Function Confirmation¶

1.2.1 COUNT Register Function Confirmation¶

The COUNT register is an internal counting register of the RTC. When the RTC clock is functioning normally, COUNT increments every second, thus serving as a preliminary judgment of the RTC clock status.

| Step | Description |

|---|---|

| A | Execute multiple reads of bank: 0x34 register |

| B | Observe whether the offset: 0x9 & 0xA registers toggle every second |

| C | If it toggles every second, it indicates that the internal counting of the RTC is normal |

1.2.2 iso flow Function Confirmation¶

As the trigger for RTC register configuration, any anomaly in iso flow will inevitably lead to abnormal RTC functionality, thus serving as a preliminary confirmation of RTC basic functionality.

| Step | Description |

|---|---|

| A | Execute riu_w 0x34 0x30 0x1 |

| B | Execute riu_r 0x34 0x31, record the value at this time as val1 |

| C | Execute riu_w 0x34 0x32 0x1 |

| D | Execute riu_r 0x34 0x31, record the value at this time as val2 |

| E | If val1=1 and val2=0, then it is normal |

2. Common Problem Analysis¶

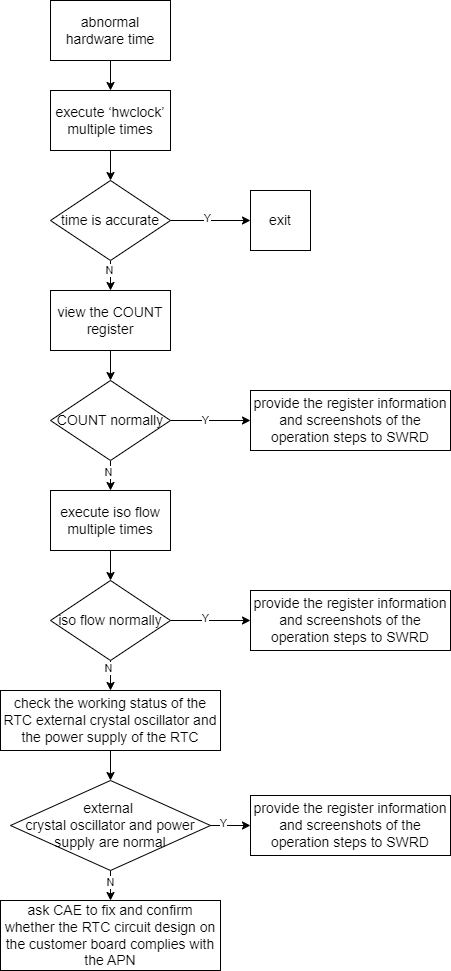

2.1 Abnormal Hardware Time Obtained¶

Refer to the debug flowchart below.

Flowchart Explanation: Check the COUNT register, please refer to 1.2.1 COUNT Register Function Confirmation.

Execute the iso flow mechanism, please refer to 1.2.2 iso flow Function Confirmation.

Provide register information to FAE, the required register is RTC BANK (0x34).

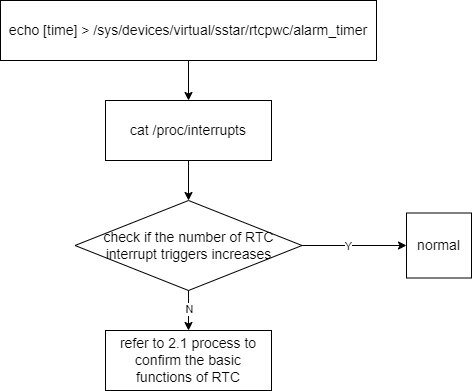

2.2 RTC Alarm Function Abnormality¶

Refer to the debug flowchart below.

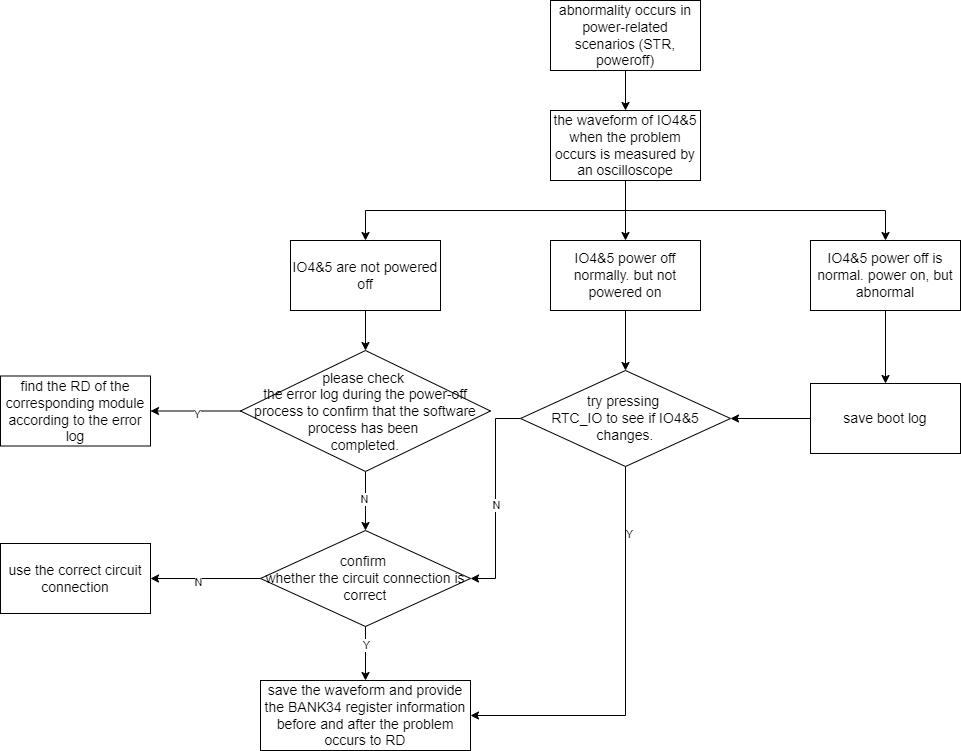

2.3 RTCPWC Function Abnormality¶

Refer to the debug flowchart for scenarios where io⅘ controls power.