EMMC USER GUIDE

REVISION HISTORY¶

| Revision No. | Description |

Date |

|---|---|---|

| 1.0 | 04/15/2025 |

1. OVERVIEW¶

MMC under Kernel adopts the standard Linux framework and can use standard interfaces to drive MMC Device (eMMC card, SD card or SDIO device).

The MMC subsystem consists of the card layer, core layer and host layer. The card layer registers the entire MMC Device as an MMC Block Device, which can support the data request work of the upper layer; the core layer implements the initialization process and reading and writing work in the MMC/SD/SDIO protocol. The host layer can mobilize the hardware and communicate the cmd or data request passed down by the core layer with the eMMC/SD/SDIO card through the FCIE/SDIO Engine.

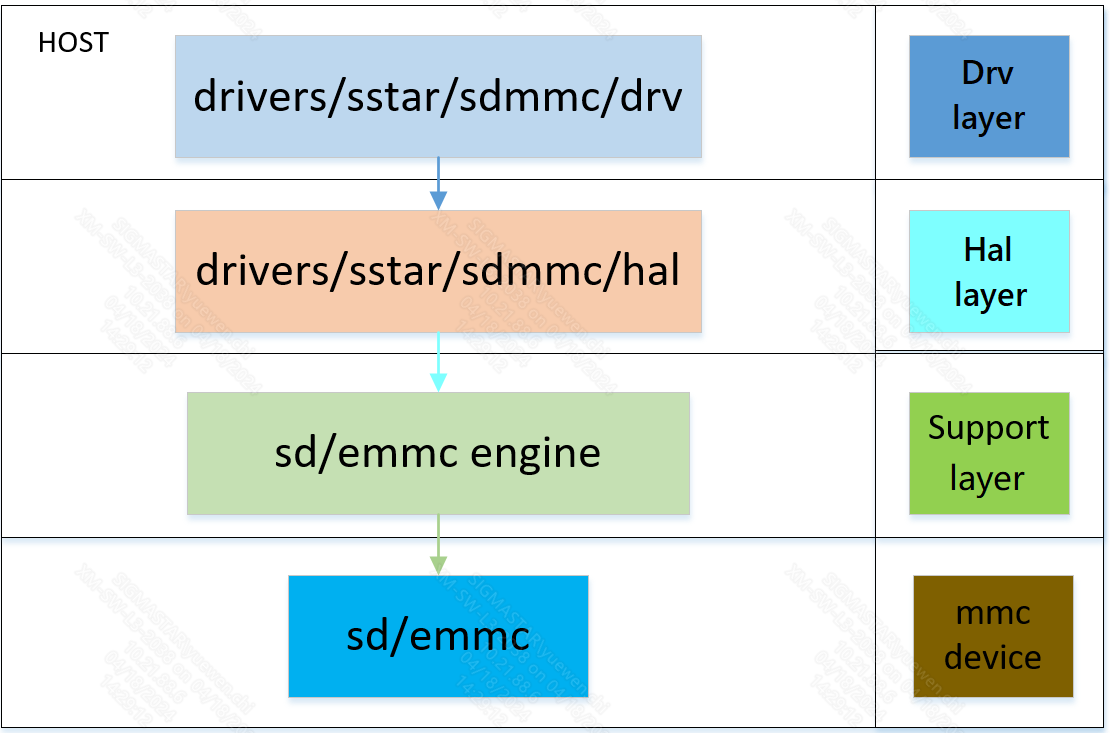

The overall framework of the eMMC host layer consists of three layers, namely the MDrv layer, the Hal layer, the Support layer, and the MMC device connected to the Support layer. The functions of each layer are as follows:

Drv layer:

The Drv layer of eMMC mainly completes the operation of registering the Host to the core layer, and also provides some additional encapsulation interfaces to set or obtain the status of the Engine and the card for the user layer, such as: eMMC_bootbus, set_sdmmc_driving_control, and completes the MIE interrupt registration to ensure the normal reception and transmission of subsequent signals, and so on.

Hal layer:

The file that implements signal transmission by reading and writing registers in the Hal layer of eMMC is hal_sdmmc_v5.c. The file that determines which group of pad pins the Host Engine connects to and performs pull-up and pull-down operations on them is hal_sdmmc_platform_common.c. The interface related to interrupt and time processing is in the hal_sdmmc_intr.c file.

Support layer:

This layer belongs to the hardware support layer, and the related final implementation of the driver requires hardware support.

MMC device:

MMC devices, such as eMMC cards, are directly connected to the driver's hardware support and are the driver's final operation object.

2. KEYWORD DESCRIPTION¶

IP: Host Engine connected to eMMC devices.

IP bank: Register address of Host Engine used by driver to access eMMC devices.

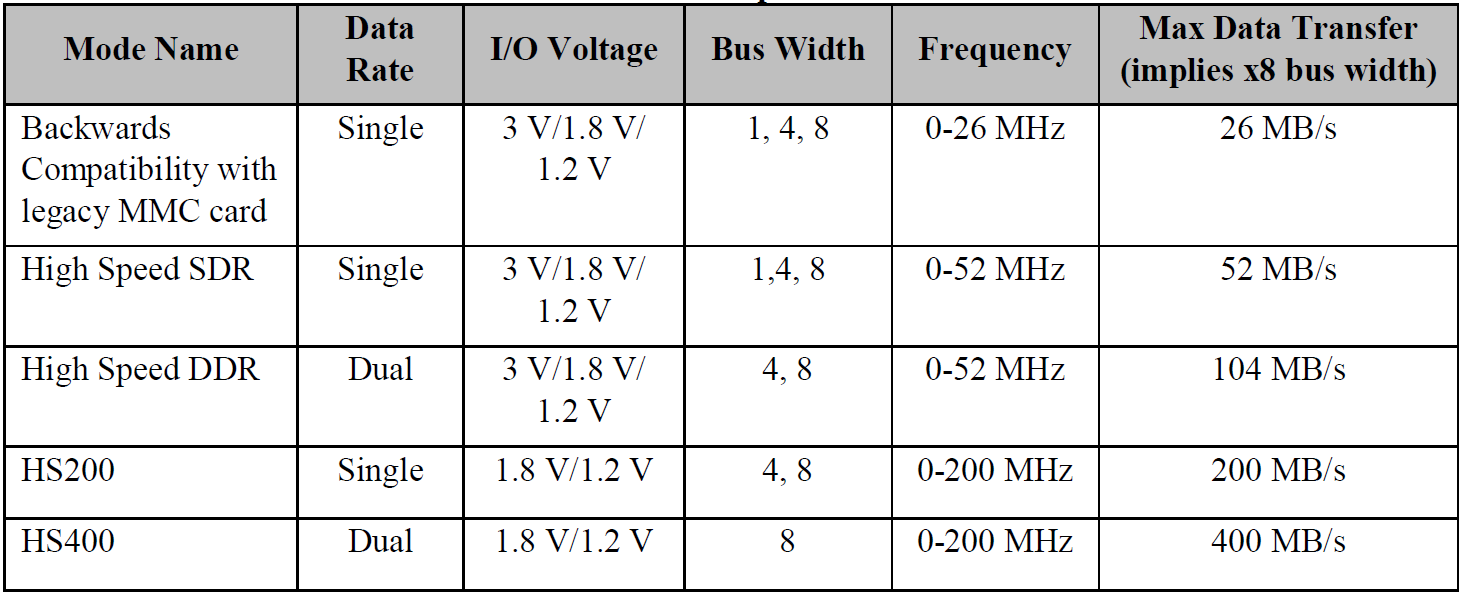

HS: High-speed interface timing mode up to 25MB/S, 50MHz single data speed bus, requires 3.3V voltage support.

HS200: High-speed interface timing mode up to 200MB/S, 200MHz single data speed bus, requires 1.8V voltage support.

HS400: High-speed DDR interface timing mode up to 400MB/s, 200MHz double data speed bus, requires 1.8V voltage support.

3. FUNCTION DESCRIPTION¶

| Package | EMMC number | Bus bandwidth | Clock range | Uboot data transfer mode | Kernel data transfer mode | IP bank | Products |

|---|---|---|---|---|---|---|---|

| BGA14 | 1 | 1, 4, 8 | 300k-200M | DMA | ADMA | 0x1410 | Pcupid |

Bus bandwidth setting:

EMMC supports three bus bandwidths: 1 -1bit mode/4 - 4bit mode / 8 - 8bit mode. The configuration method is to modify the bus-width parameter in the device tree.

Clock setting:

EMMC supports configuration of clock frequencies within the range of 300KHz-200MHz. The maximum clock can be set by modifying the max-frequency parameter in the device tree. The final set clock frequency is the maximum frequency supported by the current bus speed.

Configuring different bus bandwidths and clock frequencies will affect the data transfer speed. eMMC 5.0 supports the use of HS200 and HS400 speed modes. The default clock frequency is 200M. If you want to use it, you need to enable mmc-hs200-1_8v/mmc-hs400-1_8v in the device tree;

When configuring the High Speed SDR mode, refer to the following table for the clock frequency and theoretical speed supported by the hardware(implies x8 bus width).

| No | Clock frequency(Hz) | Transfer rate(MB/s) |

|---|---|---|

| 0 | 300000 | 3 |

| 1 | 12000000 | 12 |

| 2 | 20000000 | 20 |

| 3 | 32000000 | 32 |

| 4 | 36000000 | 36 |

| 5 | 40000000 | 40 |

| 6 | 43200000 | 43.2 |

| 7 | 48000000 | 48 |

When configuring the HS200 or HS400 speed mode, the software defaults to a 200MHz clock frequency(implies x8 bus width).

| No | Clock frequency(Hz) | Transfer rate(MB/s) |

|---|---|---|

| 0 | 200000000 (HS200) | 200 |

| 1 | 200000000 (HS400) | 400 |

Note that the actual read and write speed is affected by factors such as cmd transmission consumption and mmc device performance during the read and write process, and cannot reach the theoretical speed. To test the performance, it is recommended to use the fio tool to read and write large files for testing.

Data transfer mode settings:

EMMC supports the configuration of DMA and ADMA data transfer modes under the kernel. The ADMA mode is used by default.

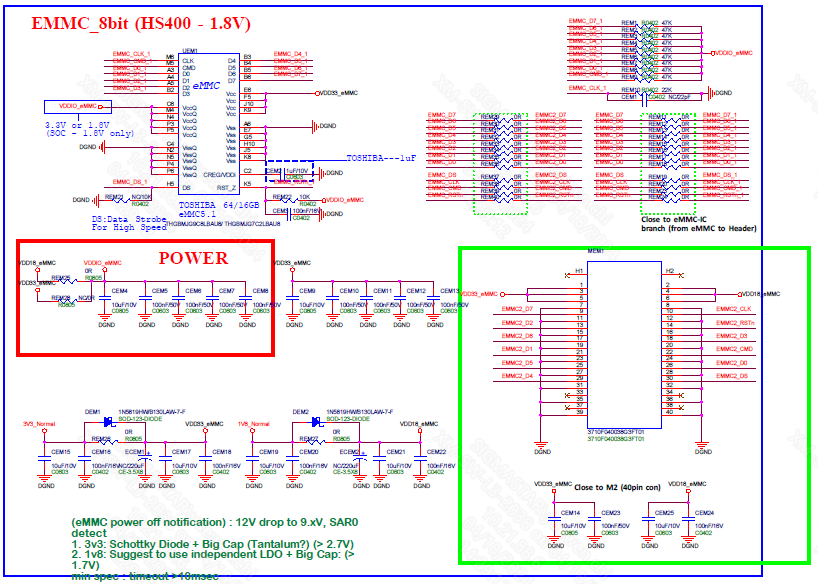

4. HARDWARE CONNECTION INTRODUCTION¶

4.1. Pcupid¶

The software padmux settings corresponding to the hardware connection are as follows:

1. padmux {

2. compatible = "sstar-padmux";

3. schematic =

4. // SDMMC0

5. <PAD_EMMC_RST PINMUX_FOR_EMMC8B_BOOT_MODE_1 MDRV_PUSE_EMMC_RST>,

6. <PAD_EMMC_CLK PINMUX_FOR_EMMC8B_BOOT_MODE_1 MDRV_PUSE_EMMC_CLK>,

7. <PAD_EMMC_CMD PINMUX_FOR_EMMC8B_BOOT_MODE_1 MDRV_PUSE_EMMC_CMD>,

8. <PAD_EMMC_D0 PINMUX_FOR_EMMC8B_BOOT_MODE_1 MDRV_PUSE_EMMC_D0>,

9. <PAD_EMMC_D1 PINMUX_FOR_EMMC8B_BOOT_MODE_1 MDRV_PUSE_EMMC_D1>,

10. <PAD_EMMC_D2 PINMUX_FOR_EMMC8B_BOOT_MODE_1 MDRV_PUSE_EMMC_D2>,

11. <PAD_EMMC_D3 PINMUX_FOR_EMMC8B_BOOT_MODE_1 MDRV_PUSE_EMMC_D3>,

12. <PAD_EMMC_D4 PINMUX_FOR_EMMC8B_BOOT_MODE_1 MDRV_PUSE_EMMC_D4>,

13. <PAD_EMMC_D5 PINMUX_FOR_EMMC8B_BOOT_MODE_1 MDRV_PUSE_EMMC_D5>,

14. <PAD_EMMC_D6 PINMUX_FOR_EMMC8B_BOOT_MODE_1 MDRV_PUSE_EMMC_D6>,

15. <PAD_EMMC_D7 PINMUX_FOR_EMMC8B_BOOT_MODE_1 MDRV_PUSE_EMMC_D7>,

16. <PAD_EMMC_DS PINMUX_FOR_EMMC8B_BOOT_MODE_1 MDRV_PUSE_EMMC_DS>,

17. };

The first column indicates the EMMC pad name, the second column indicates the pad mode, which is set according to the pad usage, and the third column is the identifier used by the driver. When using eight data lines, use PINMUX_FOR_EMMC8B_BOOT_MODE_1, and when using four data lines, use PINMUX_FOR_EMMC4B_BOOT_MODE_1.

5. UBOOT USAGE INTRODUCTION¶

5.1. Uboot Config Configuration¶

1. make menuconfig 2. # SigmaStar drivers --> 3. # <*> SigmaStar mmc host 4. # [*] SELECT EMMC

The directory of the eMMC driver under uboot is drivers/sstar/mmc_host/. To compile, you need to enable the SSTAR_MMC_HOST and SELECT EMMC compilation options. The opening method is as above.

5.2. DTS Parameter Configuration Description¶

EMMC can set the basic parameters of the host layer driver by configuring the sstar_mmc0 device node in dtsi. The parameters of dtsi are shown as follows:

sstar_mmc0: sstar_mmc0 {

compatible = "sstar-mmc";

bus-width = <8>;

max-frequency = <200000000>;

cap-mmc-highspeed = <1>;

mmc-hs400-1_8v = <1>;

mmc-hs200-1_8v = <1>;

ip-order = <2>;

pad-order = <0>;

pwr-on-delay = <10>;

pwr-off-delay = <50>;

fake-cdz = <0>;

rev-cdz = <0>;

clk-driving = <2>;

cmd-driving = <2>;

data-driving = <2>;

en-clk-phase = <0>;

rx-clk-phase = <0>;

tx-clk-phase = <0>;

non-removable = <1>;

status = "okay";

};

The definitions are as follows:

| Parameter | Definition | Remark |

|---|---|---|

| bus-width | Configure the buswidth of the card slot | 8 - 8bit mode |

| max-frequency | Configure the maximum clock frequency supported by the corresponding card slot | Uboot supports 200MHz |

| cap-mmc-highspeed | Configuration supports EMMC high speed mode | Modification prohibited |

| mmc-hs400-1_8v | Configuration supports MMC hs400 mode | UBOOT supports EMMC hs400 mode,Use requires openingCONFIG_MMC_HS400_SUPPORT |

| mmc-hs200-1_8v | Configuration supports EMMC hs200 mode | UBOOT supports EMMC hs200 mode,Use requires openingCONFIG_MMC_HS200_SUPPORT |

| ip-order | Configure the IP number of the corresponding card slot | Modification prohibited |

| pad-order | Specify which pad group the card is connected to | Public version software is not used and does not need to be modified |

| pwr-on-delay | Configure the power-on delay time of each card slot in ms | SDIO devices generally need to configure a delay time so that the SDIO device can load the firmware and the state is ready. The specific time is subject to the recommendations of the SDIO device manufacturer(EMMC/SD device nodes do not need to be modified) |

| pwr-off-delay | Configure the power-off delay time of each card slot in ms | Configure the power-on delay time of each card slot in ms |

| fake-cdz | Configure whether to ignore Card detect. Setting it to 1 means that the slot is assumed to have a card connected by default | For devices fixed on the board, such as some SDIO devices, the slot corresponding item should be configured as 1 |

| rev-cdz | This parameter can be used to configure whether to reverse the Card detect condition of the current Board | By default, the card is detected at a low level. If the hardware design shows that the CDZ level is high after the card is inserted, configure this item to 1. |

| clk-driving | Configure the driving capability of the clock pad pin of the corresponding card slot | Gear: 0-7.This item generally does not need to be modified. If you encounter communication signal quality problems, you can adjust this item based on the waveform. |

| cmd-driving | Configure the driving capability of the command pad pin of the corresponding card slot | Gear: 0-7.This item generally does not need to be modified. If you encounter communication signal quality problems, you can adjust this item based on the waveform. |

| data-driving | Configure the driving capability of the data[3:0] pad pin of the corresponding card slot | Gear: 0-7.This item generally does not need to be modified. If you encounter communication signal quality problems, you can adjust this item based on the waveform. |

| en-clk_phase | Configure whether to enable clock phase tuning for the corresponding card slot | When CRC problems occur in device read/write communications, they can be solved by changing the sampling points of rx and tx. |

| rx-clk_phase | Configure the clock tx phase of the corresponding card slot | Gear: 0-3, this parameter is valid only when en-clk_phase is set to 1, each gear phase interval is 90° |

| tx-clk_phase | Configure the clock rx phase of the corresponding card slot | Gear: 0-3, this parameter is valid only when en-clk_phase is set to 1, Each gear phase interval is 90° |

| non-removable | Configure whether the device is non-removable | No modification is required, EMMC devices need to configure this item |

Note: config needs to enable CONFIG_SSTAR_SELECT_EMMC

5.3. Uboot Cmd Parameter Description¶

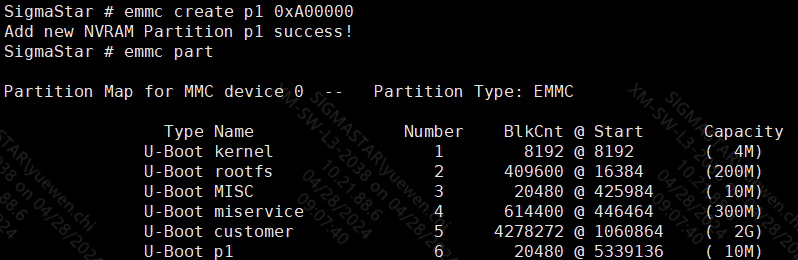

(1) emmc create

Format:

emmc create [name] [size]

Description: Create a partition, name indicates the partition name, size indicates the size (Bytes)

Example: Create a partition named p1 with a size of 10M

emmc create p1 0xA00000

(2) emmc part

Description: Display partitions in the following format: #Partition name# #Partition number# #Size@offset (occupied space), size and offset are in blocks# #Occupied space, in MBytes#

Example:

SigmaStar # emmc part

U-Boot kernela 1 20480 @ 615200 ( 10M)

U-Boot rootfsa 2 409600 @ 635680 (200M)

U-Boot usera 3 614400 @ 1045280 (300M)

U-Boot data 4 4298752 @ 1659680 ( 2G)

(3) emmc remove

Format:

emmc remove [name]

Description: Delete the partition with the specified name

Example: Delete the p1 partition

emmc remove p1

(4) emmc rmgpt

Format:

emmc rmgpt

Description: Delete all UDA partitions and remove partition information from the partition table. The UDA partition will not be erased

(5) emmc read.p

Format:

emmc read.p [addr][partition_name][size]

Description: Read partition data to memory, addr is the memory address, partition_nam is the partition name, size is the size of the copied data (Bytes)

Example: Copy 0x1000Bytes data at the beginning of p1 to memory 0x21000000

emmc read.p 0x21000000 p1 0x1000

(6) emmc write.p

Format:

emmc write.p [addr][partition_name][size]

Description: Write memory data to the eMMC partition, addr is the memory address, partition_nam is the partition name, size is the size of the copied data (Bytes)

Example: Copy 0x1000Bytes of data at the beginning of memory 0x21000000 to the eMMC p1 partition

emmc write.p 0x21000000 p1 0x1000

(7) emmc write.p.continue

Format:

emmc write.p.continue [addr] [partition_name] [offset] [size]

Description: Write memory data to the offset address of the partition, offset is the partition offset address (block unit), size is the copy data size (Bytes)

Example: Copy three split files (10M, 20M, 10M respectively) to partition p1 continuously

emmc write.p.continue 0x21000000 p1 0x0 0xA00000 //Copy 0xA00000 Bytes data to the starting address of p1 emmc write.p.continue 0x21000000 p1 0x5000 0x1400000 //0x5000=0xA00000/512 emmc write.p.continue 0x21000000 p1 0xF000 0xA00000 //0xF000=0x5000+0x1400000/512

(8) emmc read.p.continue

Format:

emmc read.p.continue [addr] [partition_name] [offset] [size]

Description: Copy the data at the partition offset to the memory

emmc read.p.continue 0x21000000 p1 0x0 0xA00000

(9) emmc erase.p

Format:

emmc erase.p [name]

Description: Format the specified partition

Example: Format the data of the p1 partition. After formatting, the partition data will be 0

emmc erase.p p1

(10) emmc erase

Format:

emmc erase

Note: Erase the entire current partition. For example, if you are currently in the UDA partition, then erase the entire UDA partition. Use with caution!

(10) mmc dev

Format:

mmc dev [dev] [part] [mode]

Description: show or set current mmc device [partition] and set mode Example 1: Switching to a UDA partition

mmc dev 0 0

Example 1: Switching to a BOOT1 partition

mmc dev 0 1

Example 3: Switching to a BOOT2 partition

mmc dev 0 2

(11) mmc erase

Format:

mmc erase blk# cnt

Description: Erase the specified data of the partition

Example 1: Erase all blocks of the user partition

mmc dev 0 0 mmc erase

Example 2: Erase 0x800 blocks starting from block 0 (use this command to erase ENV in UDA partition)

mmc dev 0 0 mmc erase 0 0x800

5.4. Uboot Cmd Use Case¶

(1) Create a new partition p1 with a size of 10M

Figure 5-1: EMMC-4

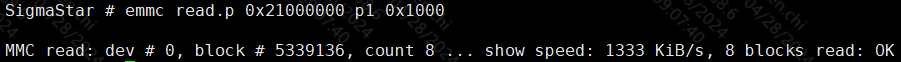

(2) Copy the 0x1000Bytes data at the beginning of p1 to the memory 0x21000000

Figure 5-2: EMMC-5

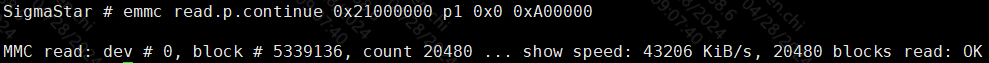

(3) Copy 0xA00000 bytes of the data at offset 0x0 of partition p1 to the memory 0x21000000

Figure 5-3: EMMC-6

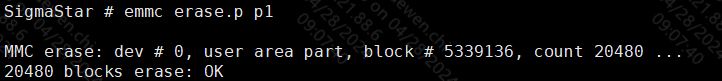

(4) Erase the data of partition p1

Figure 5-4: EMMC-7

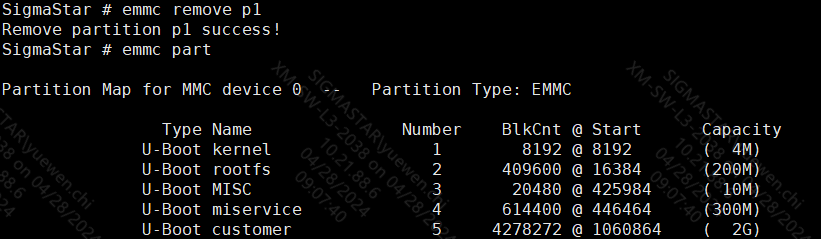

(5) Delete partition p1

Figure 5-5: EMMC-8

6. KERNEL USAGE INTRODUCTION¶

6.1. Kernel Config Configuration¶

1. Associated Driver Module

The Card layer (mmc_block.ko) and the Core layer (mmc_host.ko) use the Linux standard code, and the Host layer (kdrv_sdmmc.ko) is maintained by Sigmastar. In menuconfig, you can choose to compile them into the kernel or compile them into ko.

2. Enable the Corresponding Driver Module

1. make menuconfig 2. # Device Drivers --> 3. # <*> MMC/SD/SDIO card support --> (mmc_core.ko) 4. # <*> MMC block device driver (mmc_block.ko) 5. # [*] SStar SoC platform drivers --> 6. # <*> SStar SD/MMC Card Interface Support (kdrv_sdmmc.ko) 7. # [ ] Support SD30 8. # [*] Support EMMC50 9. # [*] Support SDMMC Command 10.# [*] Support SDMMC UT verify 11.# [*] SELECT EMMC

6.2. DTS Configuration Parameter Description¶

You can set the basic parameters of the host layer driver by configuring the sstar_sdmmc0 item in dtsi. The parameters of dtsi are shown as follows:

sstar_sdmmc0: sstar_sdmmc0 {

compatible = "sstar,sdmmc";

bus-width = <8>;

max-frequency = <200000000>;

non-removable;

broken-cd;

cap-mmc-highspeed;

mmc-hs200-1_8v;

mmc-hs400-1_8v;

no-sdio;

no-sd;

//no-mmc;

reg = <0x0 0x1F282000 0x0 0x200>;//1410

pll-reg = <0x1F283400 0x200>;//141A

cifd-reg = <0x1F282200 0x200>;//1411

pwr-save-reg = <0x1F282400 0x200>;//1412

ip-order = /bits/ 8 <2>;

pad-order = /bits/ 8 <0>;

trans-mode = /bits/ 8 <1>;

cifd-mcg-off = /bits/ 8 <0>; // mcg on/off in cifd

ssc-switch = /bits/ 8 <0>;

support-cmd23 = /bits/ 8 <1>;

//support-runtime-pm = /bits/ 8 <0>;

fake-cdz = <1>;

rev-cdz = /bits/ 8 <0>;

rev-pwr = /bits/ 8 <0>;

rev-ctrl = /bits/ 8 <0>;

cdz-pad = <PAD_GPIOE_06>;

pwr-pad = <PAD_GPIOE_07>;

pwr-on-delay = <1>;

pwr-off-delay = <30>;

dev-ctrl-delay = <1>;

sdio-use-1bit = /bits/ 8 <0>;

clk-driving = <2>;

cmd-driving = <2>;

data-driving = <2>;

en-clk-phase = /bits/ 8 <0>; //0/1

rx-clk-phase = <0>; //0-3

tx-clk-phase = <0>; //0-3

en-eight-phase = /bits/ 8 <0>; //0/1

rx-eight-phase = /bits/ 8 <0>; //0/1

tx-eight-phase = /bits/ 8 <0>; //0/1

interrupts = <GIC_SPI INT_IRQ_FCIE IRQ_TYPE_LEVEL_HIGH>,

<GIC_SPI INT_FIQ_PAD2FCIE_SD_CDZ IRQ_TYPE_LEVEL_HIGH>;

interrupt-names = "mie2_irq", "cdz_slot2_irq";

clocks = <&CLK_fcie>,<&CLK_fcie_syn>;

clock-names = "clk_sdmmc2", "syn_clk_sdmmc2";

status = "ok";

};

As shown in the figure above, the definitions of the eMMC device tree configuration nodes are:

| Parameter | Definition | Remark |

|---|---|---|

| bus-width | Configure the buswidth of the corresponding card slot | 8 - 8bit mode |

| max-frequency | Configure the maximum clock frequency supported by the corresponding card slot | |

| non-removable | Configure whether the device is non-removable. Setting 1 means that the device is non-removable by default | eMMC/SDIO devices are generally set to non-removable attributes |

| broken-cd | Configure whether to use cdz interrupt | eMMC devices do not use |

| cap-mmc-highspeed | Configure whether the device supports highspeed bus speed mode | Enable highspeed mode by default |

| mmc-hs200-1_8v | Configure whether to enable the hs200 bus speed mode | |

| mmc-hs400-1_8v | Configure whether to enable the hs400 bus speed mode | |

| no-sdio | Configure the device does not support SDIO protocol | eMMC devices do not support SDIO protocol |

| no-sd | Configure the device does not support SD protocol | eMMC devices do not support SD protocol |

| reg | Configure eMMC Host Engine Bank address | Modification prohibited |

| pll-reg | Configure eMMC Host Engine PLL Bank address | Modification prohibited |

| cifd-reg | Configure eMMC Host Engine CIFD Bank address | Modification prohibited |

| pwr-save-reg | Configure eMMC Host Engine PSM Bank address | Modification prohibited |

| ip-order | Configure the IP number of the corresponding card slot | Modification prohibited |

| pad-order | Configure the padmux mode number of the corresponding card slot | Public version software is not used and does not need to be modified |

| trans-mode | Configure the data transmission mode of the corresponding card slot | No modification required |

| fake-cdz | Configure whether the corresponding card slot ignores Card Detect | eMMC does not use, keep the default value |

| rev-cdz | Configure CDZ detection direction | eMMC does not use, keep the default value |

| rev-pwr | Configure power control direction | eMMC does not use, keep the default value. |

| rev-ctrl | Configure ctrl pin control direction | eMMC does not use, keep the default value. |

| pwr-pad | Configure the Power pin of the corresponding card slot | eMMC does not use, keep the default value. |

| cdz-pad | Configure the CDZ pin of the corresponding card slot | eMMC does not use, keep the default value. |

| pwr-on-delay | Configure the power-on delay time of the corresponding card slot | eMMC does not use, keep the default value |

| pwr-off-delay | Configure the power-off delay time of the corresponding card slot | eMMC does not use, keep the default value |

| dev-ctrl-delay | Configure the delay time before and after the ctrl pin polarity flips in ms | eMMC does not use, keep the default value. |

| ssc-switch | Configure whether to enable spread spectrum | Enable as needed |

| support-cmd23 | Configure whether to support the preset transmission block number function | Enable supporting cmd23 by default |

| support-runtime-pm | Configure whether to support runtime power management | Enable as needed |

| clk-driving | Configure the driving of the clock line of the corresponding card slot | Gear: 0-7.This item generally does not need to be modified. If you encounter communication signal quality problems, you can adjust this item based on the waveform. |

| cmd-driving | Configure the driving of the cmd line of the corresponding card slot | Gear: 0-7.This item generally does not need to be modified. If you encounter communication signal quality problems, you can adjust this item based on the waveform. |

| data-driving | Configure the driving of the data line of the corresponding card slot | Gear: 0-7.This item generally does not need to be modified. If you encounter communication signal quality problems, you can adjust this item based on the waveform. |

| en-clk-phase | Configure whether to enable clock phase tuning for the corresponding card slot | 0 - Disable / 1 - Enable |

| rx-clk-phase | Configure the clock rx four-phase of the corresponding card slot | Gear: 0-3, en-clk-phase is set to 1 to make this parameter effective |

| tx-clk-phase | Configure the clock tx four-phase of the corresponding card slot | Gear: 0-3, en-clk-phase is set to 1 to make this parameter effective |

| en-eight-phase | Configure whether the corresponding card slot enables clock 8 phase tuning | 0 - Disable / 1 - Enable |

| rx-eight-phase | Configure the clock rx eight-phase of the corresponding card slot | For details, see clk phase usage instructions. |

| tx-eight-phase | Configure the clock tx eight-phase of the corresponding card slot | For details, see clk phase usage instructions. |

| interrupts | Configure interrupt information | Modification prohibited |

| interrupt-names | Configure interrupt names | Modification prohibited |

| clocks | Configure the eMMC Host Engine clock source | Modification prohibited |

| clock-names | Configure the clock source name | Modification prohibited |

Note: config needs to enable CONFIG_SSTAR_SELECT_EMMC

clk phase instructions:

When using the four-phase mode, en-clk-phase needs to be set to 1, and then set the values of rx-clk-phase and tx-clk-phase according to the phase to be set, with a phase interval of 90°. When using the eight-phase mode, en-clk-phase and en-eight-phase need to be set to 1, and then set the values of rx-clk-phase, tx-clk-phase, rx-eight-phase and tx-eight-phase according to the phase to be set, with a phase interval of 45°.

Phase values corresponding to different phases

-

four-phase mode

phase rx-clk-phase tx-clk-phase 0° 0 0 90° 1 1 180° 2 2 270° 3 3 -

eight-phase mode

phase rx-clk-phase rx-eight-phase tx-clk-phase tx-eight-phase 0° 0 0 0 0 45° 1 0 1 0 90° 2 0 2 0 135° 3 0 3 0 180° 0 1 0 1 225° 1 1 1 1 270° 2 1 2 1 315° 3 1 3 1 -

Note 1: The default setting of hardware tx phase is 180°, so when the phase is set to 180°, the waveform of tx will be the same as when the phase is not turned on. When it is set to 0°, the phase will be 180° different from when the phase is not turned on.

-

Note 2: rx and tx can be set separately.

-

Note 3: When using the four-phase mode, the clock will be divided into four, and when using the eight-phase mode, the clock will be divided into eight. When the software setting has been turned on the phase function, the clock frequency will automatically be set to correspond to X4 and X8. When using the four-phase mode, when the clock frequency is 48M, the software sets 48M X 4, which is 192M, but the hardware is limited to no 192M clock source (as shown below), and the 108M clock source (four-division is 27M) will be used downward, so it will be downgraded. Therefore, when using a 48M clock, it is recommended to use the eight-phase mode (48M X 8 = 384M). After setting the phase, the clock frequency output is still 48M. When using other clock frequencies, you need to choose which mode to use according to the previous description.

-

Note 4: When the spread spectrum is turned on, the clock source will select spi_synth_pll. The clock frequency generated by spi_synth_pll is continuous and the setting range is 12M-266M. Therefore, if you need to output a 48M clock, you need to select the four-phase mode (the maximum clock output of the eight-phase is 266M/8 = 33M). In addition, since spi_synth_pll is also the clock source used by flash, when flash and spread spectrum need to be used at the same time, it is recommended to switch the flash clock source to spi_nonpm.

6.3. Sample Code¶

None.

6.4. Module Usage Introduction¶

After the Linux system starts, the eMMC driver is loaded normally, and after the eMMC Card is recognized, the corresponding block device node /dev/mmcblk* will be created. Use fdisk, mkfs, mount, and dd tools to apply for partitions, format partitions, mount partitions, and read and write mounted partitions for MMC devices.

In addition, the driver provides sysfs for debugging. You can enter the /sys/class/mmc_host/mmc0/device/ directory to perform operations:

1. cd /sys/class/mmc_host/mmc0/device/ 2. 3. # View eMMC Host clock frequency 4. cat debug_get_sdmmc_clock 5. 6. # View the last communication status between eMMC Host and Device 7. cat debug_get_sdmmc_status 8. 9. # Set the bootbus value of [slotNo] eMMC 10. echo [slotNo] [bootbus] > eMMC_bootbus 11. # View the bootbus value of eMMC in all slots 12. cat eMMC_bootbus 13. 14. # Erase the eMMC Device by specifying the starting position and number of blocks 15. echo [startblkAddr] [blkcnt] > eMMC_erase 16. 17. # Set [slotNo] eMMC Device to support HW reset 18. echo [slotNo] > eMMC_hwreset 19. # Check whether the eMMC Device enables HW reset support 20. cat eMMC_hwreset 21. 22. # Set the boot partition of eMMC Device 23. echo [partconf] > eMMC_partconf 24. #[partconf] -0: don't support boot 25. # -1: boot0 partition 26. # -2: boot1 partition 27. # -7: UDA 28. # View the boot partition of eMMC Device 29. cat eMMC_partconf 30. 31. # Set eMMC write protection range (by group) 32. echo [otption] [address] <size> > eMMC_write_protect 33. #[option] -0: Set the eMMC address of the group to be 'write protect' 34. # -1: Clear the eMMC address of the group remove 'write protect' 35. # -2: Ask the eMMC address of the group whether it's in 'write protect'? 36. # -3: ASK the eMMC address of the group about the 'write protect' type 37. #[address] Unit: block 38. #[size] Unit: block 39. 40. 41. # Hard reset [slotNo] eMMC Device 42. echo [slotNo] > sdmmc_reset 43. 44. 45. # Set the driver capability of the eMMC pin 46. echo [slotIndex] [signalLine] [drvLevel > set_sdmmc_driving_control 47. echo [slotIndex] [drvLevel] > set_sdmmc_driving_control 48. echo [signalLine] [drvLevel] > set_sdmmc_driving_control 49. echo [drvLevel] > set_sdmmc_driving_control 50. #[slotIndex]: 0-1 51. #[signalLine]: "clk"/"cmd"/"data"/"all" 52. #[drvLevel]: 0-7 53. 54. # Set the spread spectrum parameters 55. ssc set param usage: 56. 1. echo [slotIndex] [modulation] [deviation] > sdmmc_setssc 57. operation [slotIndex] is slot number:0-2. 58. operation [modulation] value is between [20, 40], origin default is 20 59. operation [deviation] value is between [1000, 3001], origin default is 3001 60. e.g. echo 0 20 1001 > sdmmc_setssc 61. 2. echo [slotIndex] [disable ssc] > sdmmc_setssc 62. disable: e.g. echo 0 0 > sdmmc_setssc 63. enable: e.g. echo 0 1 > sdmmc_setssc 64. 65. # Set the clock phase 66. set phase param usage: 67. 1. echo [mode] [tx-clk-phase] [rx-clk-phase] [tx-eight-phase] [rx-eight-phase] > sdmmc_clk_phase 68. operation [mode] is phase mode:4 or 8 69. operation [tx/rx-clk-phase] value is between [0, 3] 70. operation [tx/rx-eight-phase] value is between [0, 1] 71. e.g. Four-phase mode(180°): 72. echo 4 2 2 > sdmmc_clk_phase 73. e.g. Eight-phase mode(180°): 74. echo 8 0 0 1 1 > sdmmc_clk_phase 75. 2. echo [enable/disable clk phase] > sdmmc_clk_phase 76. disable: e.g. echo 0 > sdmmc_clk_phase 77. enable: e.g. echo [4/8] > sdmmc_clk_phase

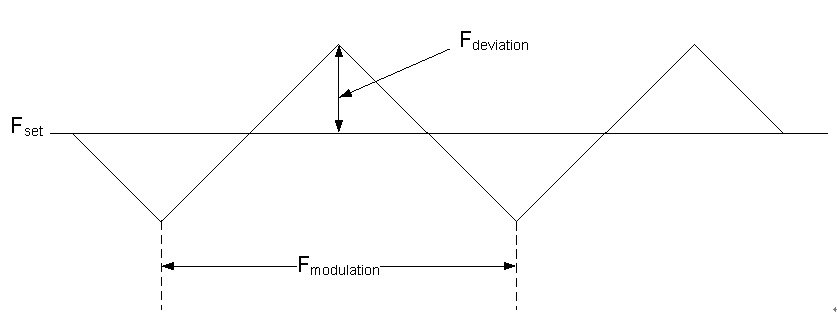

Spread spectrum parameter usage instructions:

There are 3 parameters which may affect the modulation rate of SSC function: SET, SPAN and STEP.

-

PLL_SET = (MPLL*524288)/(SYN_CLK)

SPAN (14 bits)

STEP (12 bits)

SPAN = (MPLL * 131072) / (PLL_SET * Fmodulation)

STEP = (PLL_SET * Rdeviation) / SPAN

Fmodulation is the modulation frequency of SSC, it’s range is (20KHz ~ 40KHz)

Rdeviation is the deviation of SSC.(the max range is +-3 %)

Example:

Set the spread spectrum modulation frequency to 40KHz and the deviation to +-1%

echo 0 40 1000 > sdmmc_setssc

-

SYN_CLK = 75Mhz

ref_clk = 432Mhz

Modulation is 40KHz

Deviation is 1%

SET = ( 432MHz * 524288) / (75MHz ) = 3019899 = 0x2E147B

SPAN = (432MHz * 131072)/ ( 3019899 * 40KHz) = 468 = 0x1D4

STEP = (3019899 * 1%) /468 = 64 = 0x40

7. API REFERENCE¶

This function module needs to open the CONFIG_SUPPORT_SDMMC_COMMAND configuration item and provide the following interfaces:

| API name | Function |

|---|---|

| SDMMC_Init | Initialize the eMMC driver and identify the device |

| SDMMC_WriteData | Write data to the eMMC device |

| SDMMC_ReadData | Read data from the eMMC device |

| eMMC_EraseBlock | Erase the specified data in the eMMC device |

| eMMC_GetExtCSD | Get the ExtCSD register content of the eMMC device |

7.1. SDMMC_Init¶

-

Purpose

Initialize eMMC driver and identify device.

-

Syntax

U16_T SDMMC_Init(struct sstar_sdmmc_slot *p_sdmmc_slot)

-

Parameter

Parameter name Description p_sdmmc_slot The control block corresponding to eMMC is generated when the driver is registered and added to the mmc_host private variable -

Return value

Return value Description 0 Success other Failure

7.2. SDMMC_WriteData¶

-

Purpose

Write data to the eMMC device.

-

Syntax

U16_T SDMMC_WriteData(struct sstar_sdmmc_slot *p_sdmmc_slot, U32_T u32CardBlkAddr, U16_T u16BlkCnt, U8_T *pu8DataBuf)

-

Parameter

Parameter name Description p_sdmmc_slot The control block corresponding to eMMC is generated when the driver is registered and added to the mmc_host private variable u32CardBlkAddr Block address written to eMMC u16BlkCnt Number of blocks written pu8DataBuf Cache address of the data to be written -

Return value

Return value Description 0 Success other Failure

7.3. SDMMC_ReadData¶

-

Purpose

Read data from EMMC.

-

Syntax

U16_T SDMMC_ReadData(struct sstar_sdmmc_slot *p_sdmmc_slot, U32_T u32CardBlkAddr, U16_T u16BlkCnt, U8_T *pu8DataBuf)

-

Parameter

Parameter name Description p_sdmmc_slot The control block corresponding to eMMC is generated when the driver is registered and added to the mmc_host private variable u32CardBlkAddr Block address read from eMMC u16BlkCnt Number of blocks read pu8DataBuf Cache address for storing data -

Return value

Return value Description 0 Success other Failure

7.4. eMMC_EraseBlock¶

-

Purpose

Erase the data at the specified address in the eMMC.

-

Syntax

U16_T eMMC_EraseBlock(struct sstar_sdmmc_slot *p_sdmmc_slot, U32_T u32BlkAddrStart, U32_T u32BlkAddrEnd)

-

Parameter

Parameter name Description p_sdmmc_slot The control block corresponding to eMMC is generated when the driver is registered and added to the mmc_host private variable u32BlkAddrStart Start address of erasing u32BlkAddrEnd End address of erasing -

Return value

Return value Description 0 Success other Failure

7.5. eMMC_GetExtCSD¶

-

Purpose

Get the ExtCSD register content of the eMMC device.

-

Syntax

U16_T eMMC_GetExtCSD(struct sstar_sdmmc_slot *p_sdmmc_slot, U8_T *pu8DataBuf)

-

Parameter

Parameter name Description p_sdmmc_slot The control block corresponding to eMMC is generated when the driver is registered and added to the mmc_host private variable pu8DataBuf Cache address for saving the ExtCSD content -

Return value

Return value Description 0 Success other Failure

8. DEBUG & FAQ¶

The error code types printed in the log when an exception occurs are:

(1)SD_STS:0xFF01 Read CRC error

(2)SD_STS:0xFF02 Write CRC error

(3)SD_STS:0xFF04 Write data timeout

(4)SD_STS:0xFF08 Command sent but no response

(5)SD_STS:0xFF10 Command response has CRC error

(6)SD_STS:0xFF20 Read data timeout

(7)SD_STS:0xFF40 Device is busy

According to the actual problems that the eMMC card may encounter, it is divided into the following types:

1. Card recognition failure

If the card recognition fails, it is necessary to determine whether the response acquisition fails or the transmission signal is not good and there is a CRC problem. The problem can be determined by capturing the waveform. The specific difference and debug method are as follows:

-

Response acquisition failure

Phenomenon: There is only a command sent by the host on the waveform, and no response returned by the device.

Debug method: First, determine whether the voltage and clock are normal, and then check whether there is a command sent on the waveform. If there is no problem with the first two, then determine whether the card has a reply response. If there is no response, check the device status.

-

Bad signal with CRC problem

Phenomenon: If the command and response are normal from the waveform, consider the CRC problem.

Debug method: If there is a CRC problem, first eliminate the hardware problem, such as: whether the device contact is good, whether there is external interference, etc. Then try to change the driving gear in the dts. If there is still a problem, you need to consider adjusting the clock phase.

2. Read and write failure

If you encounter problems during normal reading and writing, you need to determine whether it is a read and write timeout problem or a bad signal with CRC problem. You can distinguish the problems through log. The timeout problem has the word timeout. The debug method is as follows:

-

Read and write timeout

Phenomenon: The word timeout is in the error log.

Debug method: First, you need to determine whether the current clock frequency and bus width are the expected configuration values. Secondly, you can increase the timeout time in the driver and try again. If there is still a timeout problem, you need to capture the waveform for detailed analysis.

-

Bad signal with CRC problem

Phenomenon: If the above problems are excluded, it may be a CRC problem.

Debug method: The debug method is as mentioned above. In addition, for CRC problems during reading and writing, if the speed requirement is not very high, you can consider reducing the frequency or bus width.

9. EMMC MASTER CHIP PRODUCTION AND BURNING DESCRIPTION¶

9.1. Introduction¶

emmcnize is a tool for making emmc master chip images, which is used to merge kernel, rootfs, file system, user data, environment variables and other images into an image that can be directly burned to a blank chip through a burner.

emmcnize tool:

9.2. Usage Method¶

Put the images to be packaged (env.bin, kernel, rootfs.ext4, data.ext4, etc.) and UDA partition configuration file (part.ini) in the same directory as the emmcnize tool, specify the configuration file as input, specify the output file, format: ./emmcnize (input ini file) (output image file), for example:

./emmcnize part.ini image.bin -b 0x2000

As mentioned above, part.ini is the partition configuration file, image.bin is the output complete image, 0x2000 is the starting address of the user partition.

9.2.1 part.ini Configuration File Format¶

[env] image=env.bin vol_id=0 vol_size=0x3B1000 vol_name="" [kernel-volume] image=kernel vol_id=1 vol_size=0xA00000 vol_name=kernel [rootfs-volume] image=rootfs.ext4 vol_id=2 vol_size=0xC800000 vol_name=rootfs [MISC-volume] image=misc.fwfs vol_id=3 vol_size=0xA00000 vol_name=MISC [miservice-volume] image=miservice.ext4 vol_id=4 vol_size=0x12C00000 vol_name=miservice [customer-volume] image=customer.ext4 vol_id=5 vol_size=0x82900000 vol_name=customer

image=XX, defines the partition image name, which must be the same as the existing image name.

vol_id=X, defines the partition id, starting from 1 to identify the partition number, and 0 means it is not included in the partition management.

vol_size=XX, defines the partition size (bytes), which must not be less than the corresponding image size.

vol_name=XX, defines the partition name, the partition name seen by the emmc part under uboot.

[XXX-volume] section is the real user partition, and their image, vol_size, and vol_name can be changed according to the actual partition situation. vol_id is numbered from 1 and supports up to 64 partitions.

9.2.2 Create Environment Variable Images¶

Except for env.bin, all other images are compiled and generated. To create env.bin, the environment variables to be set are written into a txt file in the format printed by the uboot printenv command, for example:

#env.txt baudrate=115200 bootargs=console=ttyS0,115200 root=/dev/mmcblk0p2 rootwait rootfstype=ext4 rw init=/linuxrc cma=64M bootcmd=emmc read.p 0x21000000 kernela 0x1C61E8;bootm 0x21000000; bootdelay=0 ethact=sstar_emac ethaddr=00:30:1b:ba:02:db fileaddr=23b2ef00 filesize=101 stderr=serial stdin=serial stdout=serial

After uboot is compiled, there is a mkenvimage tool in the tool directory. The command parameters are as follows:

./tools/mkenvimage

Please specify the size of the environment partition.

mkenvimage [-h] [-r] [-b] [-p <byte>] -s <environment partition size> -o <output> <input file>

This tool takes a key=value input file (same as would a `printenv' show) and generates the corresponding environment image, ready to be flashed.

The input file is in format:

key1=value1

key2=value2

...

Empty lines are skipped, and lines with a # in the first

column are treated as comments (also skipped).

-r : the environment has multiple copies in flash

-b : the target is big endian (default is little endian)

-p <byte> : fill the image with <byte> bytes instead of 0xff bytes

-V : print version information and exit

If the input file is "-", data is read from standard input

Execute ./mkenvimage -s 0x1000 -o env.bin env.txt to generate the environment variable image. The unit of size is byte, and its size should be the same as CONFIG_ENV_SIZE of uboot, otherwise there will be a CRC check failure problem.

9.2.3 Description¶

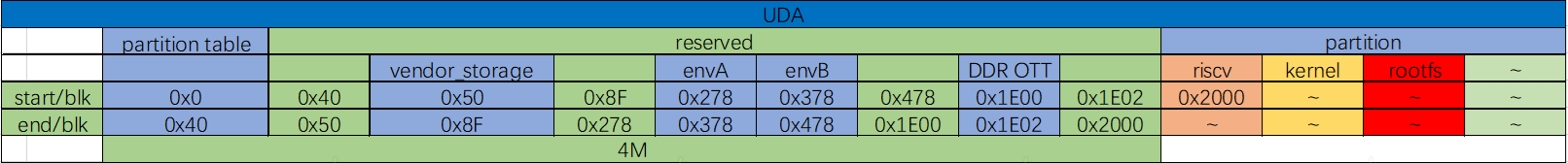

The size of env in the part.ini file is larger than the actual size of env.bin. This is because when the master chip tool makes the master chip, it will start to supplement the image file from the starting address 0x278 of env until the size of the current partition is supplemented. If it is burned according to the actual size of env.bin, 0x278*512+0x1000=327680 byte=640 blk will be the place where the user partition data starts to be stored. This is different from the actual starting address of the user data read under our uboot. The address of reading the corresponding data under uboot is as follows:

Figure 9-1: EMMC-9

As shown above, the starting address of UDA partition 1 is 0x2000 (the actual address should be based on the partition address set by the user, where partition 1 is riscv). In order to ensure that the corresponding data can be read correctly under uboot, the size of env in part.ini needs to be set to 0x2000-0x278=0x1D88 blk=0x3B1000 byte.

9.2.4 Others¶

You can view other functions of emmcnize by typing emmcnize -h.

./emmcnize -h

emmcnize This tool takes a ini image layout input file and generates the corresponding image that ready to be flashed.

./emmcnize <input ini file> <output image file> [b|p|v|h]

The input file is in format:

[<name>-volume]

image=<bin file name>

vol_id=XX

vol_size=<partition size in bytes in hex>

vol_name=<partition name>

-p :only generate partition table image:

-b :redefine the start offset block of user's partition(unit: blk)

-h :help

-v :print version information and exit

9.3. Master Chip Burning¶

Cut the emmc partition to the UDA partition, and then burn image.bin (generated in the previous section) to address 0.

If you think the master chip is too large and the burning is too slow, you can also cut the master chip into small files according to a certain size. The script is as follows:

#!/bin/sh FLASH_BLK_SIZE=$((512)) SPLIT_SIZE=$((0x1400000)) #split_size_16=0x`echo "obase=16;$SPLIT_SIZE" |bc ` split_size_16=0xA000 echo "split size:" $SPLIT_SIZE SRC_FILE=$1 BURN_SCPT=burn.es OUT_DIR=output rm -rf $OUT_DIR mkdir $OUT_DIR IMAGE_SIZE=`stat --format=%s $SRC_FILE` echo "image size: " $IMAGE_SIZE if [ $IMAGE_SIZE -gt $SPLIT_SIZE ]; then echo -e "\e[1;32m $SRC_FILE too large, size($IMAGE_SIZE) do split($SPLIT_SIZE)! \e[0m" offset_blk=0 split -b $SPLIT_SIZE $SRC_FILE $OUT_DIR/${SRC_FILE}_ for i in `ls $OUT_DIR/$SRC_FILE_*` do offset_blk_16=0x`echo "obase=16;$offset_blk"|bc` file=`basename $i` echo "tftp 0x21000000 $file" >> $OUT_DIR/$BURN_SCPT #echo "emmc write 0x21000000 $offset_blk_16 $split_size_16" >> $OUT_DIR/$BURN_SCPT file_size=`stat --format=%s $i` if [ $SPLIT_SIZE -gt $file_size ]; then file_size=$(($file_size/$FLASH_BLK_SIZE)) split_size_16=0x`echo "obase=16;$file_size" |bc ` else split_size_16=0xA000 fi echo "mmc write 0x21000000 $offset_blk_16 $split_size_16" >> $OUT_DIR/$BURN_SCPT IMAGE_BLK_SIZE=$(($SPLIT_SIZE/$FLASH_BLK_SIZE)) offset_blk=$(($offset_blk + $IMAGE_BLK_SIZE)) done echo "% <- this is end of file symbol" >> $OUT_DIR/$BURN_SCPT fi

Execution command format: ./split_burn_emmc.sh image.bin, where image.bin is the master chip, and the final cut files are in the output directory.

9.4. Configure EMMC ECSD Registers¶

Note: Related read and write operations require a special tool. Please contact the corresponding emmc manufacturer for it.

1. Configure erase group define, reliable write, that is

| EXT-CSD address | Setting value |

|---|---|

| [175] | 0x01 |

| [167] | 0x1F |

| [155] | 0x01 |

After the setting is completed, you need to power off the emmc and then power it on again, otherwise the configuration will not take effect.

2. Configuration will be required when burning the boot1 partition and the boot data is stored in the boot1 partition

| EXT-CSD address | Setting value |

|---|---|

| [162] | 0x01 |

| [177] | Must be configured according to the actual boot method |

| [179] | 0x09 |

3. Configuration will be required when burning the UDA partition and the boot data is stored in the boot1 partition

| EXT-CSD address | Setting value |

|---|---|

| [162] | 0x01 |

| [177] | Must be configured according to the actual boot method |

| [179] | 0x08 |

4、EXT-CSD configuration description

1) Reliable Write must be set. If not, the data written on the eMMC may be damaged when the power is off. However, some eMMCs have Reliable Write enabled by default. If ecsd[167] is 0x1f, Reliable Write does not need to be set. If Reliable Write cannot be set, please consult the eMMC manufacturer.

2) EXT-CSD[179] = 0x8, boot data is stored in boot1, set the boot1 partition as the boot partition. If the boot1 partition is not selected as the boot partition, be sure to select the boot data storage partition as the boot partition. For example, if the boot data is stored in boot2, it should be configured as 0x10. If the boot data is stored in UDA, it should be configured as 0x38.

3) The value of EXT-CSD[177] must be configured according to the actual boot mode. For example, if the boot type is eMMC 8-bit boot, it needs to be configured to 0x02. If the boot type is eMMC 4-bit boot, it needs to be configured to 0x01.

4) If the EXT-CSD[162] of some eMMCs is not set to 1, the system will not boot, so it must be set. ECSD[162]=1 requires eMMC to check the HW reset pin. The default value is 0, which means it will not be checked.