Gpio_DebugSop

REVISION HISTORY¶

| Revision No. | Description |

Date |

|---|---|---|

| 1.0 | 12/19/2024 |

前言¶

本文为FAE及软件开发相关人员而写,旨在介绍开发过程中客户遇到GPIO相关问题时,如何自行进行初步排查,确定是Sigmastar问题后再提供相关信息给RD分析。

1. Debug常用的基本操作和命令¶

1.1 echo 命令¶

支持userspace通过echo指令进行GPIO的申请、电平模式的配置、复用功能冲突查询等操作。详见GPIO使用参考 4.3章节

1.2 HW checklist有关GPIO的使用说明¶

本小节主要说明HW checklist中GPIO部分与riu_r/w指令的联动使用

1.2.1 配置说明¶

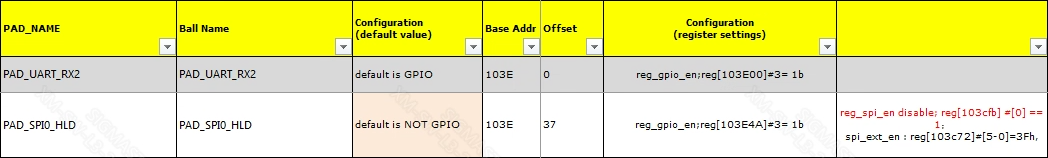

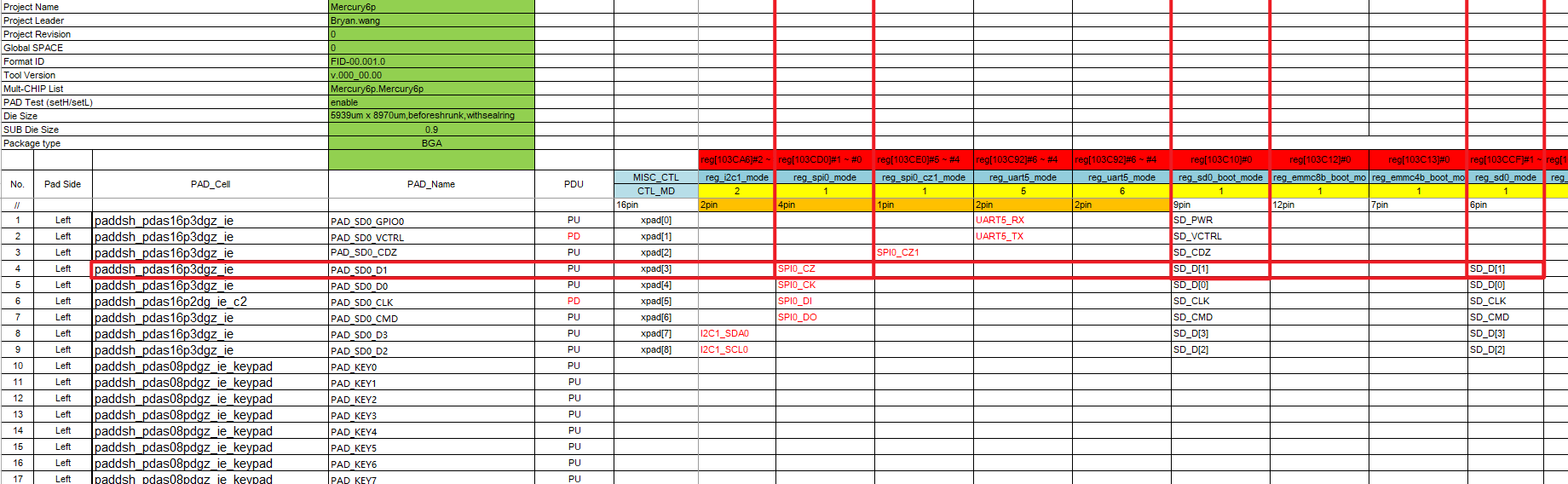

HW checklist中包含所有可当作GPIO使用的引脚,表格里面有其引脚信息,包括引脚默认状态、输入寄存器地址、输出寄存器地址、调节驱动能力寄存器地址、上拉寄存器地址、下拉寄存器地址等。以下说明图文仅为举例,具体寄存器配置以对应平台release的文件为准

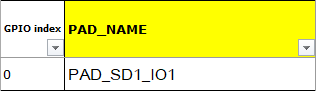

GPIO index和PAD_NAME是引脚最基本的信息,分别表示GPIO索引号和名称

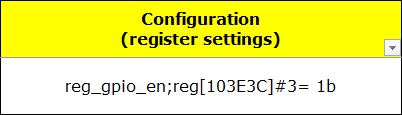

Configuration(register settings)表示将引脚设为GPIO MDOE所需要操作的寄存器,以下图为例,则表示如果要将此根引脚当作GPIO的话需要将寄存器[103E3C]中的BIT3写1,下文以con_bit代替

reg[103E3C]表示需要操作的寄存器的Bank Addr为0x103E,Offset Addr为(0x3C)/ 2 = 0x1E

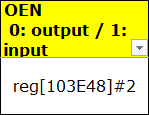

OEN表示引脚在GPIO MODE下的direction的寄存器,0表示output,1表示input,以下图为例,则表示需要查看寄存器[103E48]中的BIT2,下文以oen_bit代替

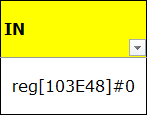

IN表示GPIO在input模式下的电平值,0表示低电平,1表示高电平,以下图为例,则表示需要查看寄存器[103E48]中的BIT0,下文以in_bit代替

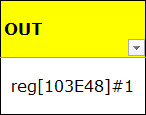

OUT表示GPIO在output模式下的电平值0表示低电平,1表示高电平,以下图为例,则表示需要查看寄存器[103E48]中的BIT1,下文以out_bit代替

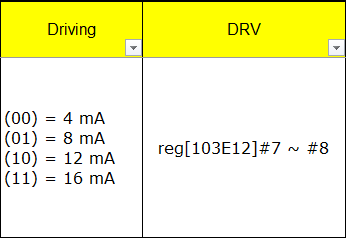

Driving和DRV表示引脚的驱动能力信息,Driving表示引脚的驱动能力等级的具体挡位,DRV则表示调节驱动能力等级所需操作的寄存器,以下图为例,表示这只脚有的驱动能力有四档分别是4mA、8mA、12mA、16mA,可通过寄存器[103E12]的BIT7、BIT8进行操作

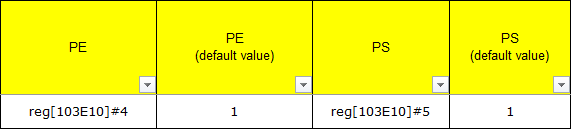

PE和PS表示调节引脚内部上下拉所需操作的寄存器,PE(default value)和PS(default value)则表示对应寄存器默认的值。以下图为例,调节引脚内部上下拉需要操作的寄存器为[103E10]的BIT4、BIT5

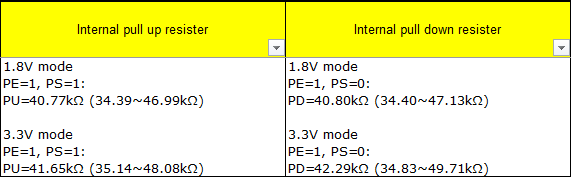

具体PE和PS值为多少的时候是上拉下拉状态可以通过下面两列进行确认,可以看到这里PE=1,PS=1的时候为上拉;PE=1,PS=0的时候为下拉

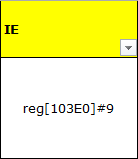

IE表示Input-Enable,针对的是该引脚的输入功能,任何涉及输入的复用功能都需要设置该bit,切忌与OEN的input混淆。IE默认是使能状态

1.2.2 控制GPIO状态¶

| 步骤 | 说明 |

|---|---|

| A | 获取到HW checklist |

| B | 找到要操作的引脚的Configuration(register settings)信息,可以得到bank、offset以及对应的con_bit,详见1.2.1 配置说明 |

| C | 找到要操作的引脚的OEN信息,可以得到bank、offset以及对应的oen_bit,一般情况下,这里的bank和offset与步骤B一致,详见1.2.1 配置说明 |

| D | 找到要操作的引脚的OUT信息,可以得到bank、offset以及对应的out_bit,详见1.2.1 配置说明 |

| E | 找到要操作的引脚的IN信息,可以得到bank、offset以及对应的in_bit,详见1.2.1 配置说明 |

| F | riu_r bank offset,获取到该引脚操作之前的GPIO状态 |

| G | 根据步骤F获取到的value,修改con_bit、oen_bit、out_bit、in_bit对应的bit位,注意!不要动到该offset下其他的bit位 output-high: con_bit=1、oen_bit=0、out_bit=1 output-low: con_bit=1、oen_bit=0、out_bit=0 input: con_bit=1、oen_bit=1 |

| H | 将修改后的值通过riu_w写入:riu_w bank offset value |

1.2.3 获取GPIO使能状态¶

| 步骤 | 说明 |

|---|---|

| A | 获取到HW checklist |

| B | 找到要操作的引脚的Configuration(register settings)信息,可以得到bank、offset以及对应的con_bit,详见1.2.1 配置说明 |

| C | riu_r bank offset,获取到该引脚目前的GPIO状态,如果con_bit的状态符合HW checklist所述,则表示GPIO mode已使能,反之 |

| D | 需要进一步获取当前引脚的输入输出模式以及电平状态可以继续往下看步骤E |

| E | 找到要操作的引脚的OEN信息,可以得到bank、offset以及对应的oen_bit,oen_bit=1表示input,oen_bit=0表示output |

| F | 找到要操作的引脚的OUT信息,可以得到bank、offset以及对应的out_bit,out_bit=1表示output-high,oen_bit=0表示output-low |

| G | 找到要操作的引脚的IN信息,可以得到bank、offset以及对应的in_bit,in_bit表示当前引脚真实的外部电平,因此如果发现output模式下,in_bit和out_bit的值不相等,说明该引脚电平状态是异常的 |

流程B涉及到的Configuration(register settings)信息,在大部分引脚上只对应一个寄存器地址,但存在着引脚Configuration信息是对应多个寄存器,具体情况可以在HW checklist中查询,总体思路无异,同样是确认这些寄存器对应bit是否使能

1.2.4 控制GPIO内部上下拉¶

| 步骤 | 说明 |

|---|---|

| A | 获取到HW checklist |

| B | 找到要操作的引脚的PE信息,可以得到bank、offset以及对应的pe_bit,详见1.2.1 配置说明 |

| C | 找到要操作的引脚的PS信息,可以得到bank、offset以及对应的ps_bit,详见1.2.1 配置说明 |

| D | 找到Internal pull up register和Internal pull down register,确定上下拉情况下PE和PS的状态,详见1.2.1 配置说明 |

| E | riu_r bank offset,获取到该引脚操作之前的GPIO状态 |

| F | 根据步骤E获取到的value,修改pe_bit、ps_bit对应的bit位,注意!不要动到该offset下其他的bit |

| G | 将修改后的值通过riu_w写入:riu_w bank offset value |

GPIO上下拉状态的查询也可以依照此法

1.2.5 调节GPIO驱动能力¶

| 步骤 | 说明 |

|---|---|

| A | 获取到HW checklist |

| B | 找到要操作的引脚的DRV信息,可以得到bank、offset以及对应的drv_bit[m,n],详见1.2.1 配置说明 |

| C | 找到要操作的引脚的Driving信息,可以得到当前引脚所支持的驱动能力等级 |

| D | riu_r bank offset,获取到该引脚操作之前的GPIO状态 |

| E | 根据步骤D获取到的value,将所要设置的驱动能力等级写入drv_bit[m,n]对应的bit位,注意!不要动到该offset下其他的bit |

| F | 将修改后的值通过riu_w写入:riu_w bank offset value |

GPIO当前驱动能力的查询也可以依照此法

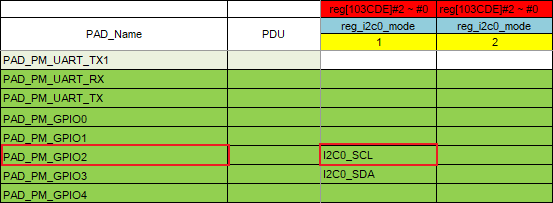

1.3 Tmux_Table使用说明¶

Tmux_Table是所有的复用功能的汇总,当需要将某只引脚设为某个特定的复用功能,可以到这份table中查询具体需要操作的bank,offset以及bit

1.3.1 复用功能的寄存器配置¶

以下图举例说明复用功能的寄存器操作步骤

| 步骤 | 说明 |

|---|---|

| A | 获取到Tmux_Table |

| B | 找到要操作的引脚:PAD_PM_GPIO2,要设置的复用功能:I2C0_SCL |

| C | 横纵定位之后可以看到要操作的寄存器是reg[103CDE]#2~#0,可以确定bank:103C offset:DE/2=6F bit[2:0] |

| D | 查询reg[103CDE]#2~#0同列下方的mode数,即图上黄底位置,为1,表示bit[2:0]写1 |

| E | riu_r bank offset,获取到该寄存器的值 |

| F | 根据步骤D获取到的value,修改bit[2:0]的值为1,注意!不要动到该offset下其他的bit |

| G | 将修改后的值通过riu_w写入:riu_w bank offset value |

引脚当前复用功能的查询也可以依照此法

1.3.2 复用功能的冲突检查¶

方法一(借助Tmux_Table):

| 步骤 | 说明 |

|---|---|

| A | 获取到Tmux_Table |

| B | 找到要查询的引脚在Tmux_Table中对应的行 |

| C | 根据上文1.3.1提到的方法,确认该引脚所有复用功能的使能状态 |

| D | 根据上文1.2.3提到的方法,确认该引脚GPIO mode的使能状态 |

| E | 全部功能查询完成之后,就可以得知当前是否有多种复用功能使能 |

方法二(借助drivers/sstar/gpio/chip_name/hal_pinmux.c):

| 步骤 | 说明 |

|---|---|

| A | 进入hal_pinmux.c |

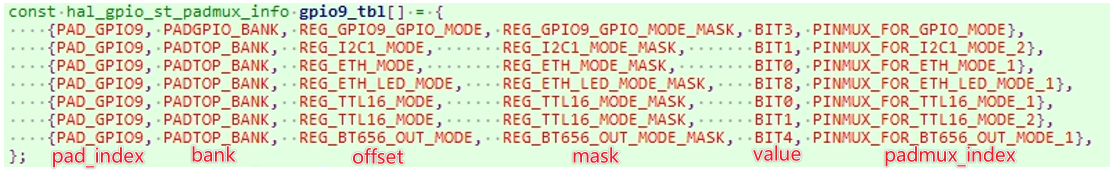

| B | 找到要查询的引脚对应的数组,数组包含了设置复用功能的相关宏定义:bank offset mask value |

| C | 根据数组中复用功能从上至下查询 |

| D | 全部复用功能查询完成之后,就可以得知当前是否有多种复用功能使能 |

以上图为例:如果要查询当前引脚的I2C1_MODE_2是否使能 可以在代码中查询到

#define PAD_GPIO9 17 #define PADTOP_BANK 0x103C00 #define REG_I2C1_MODE 0x53 #define REG_I2C1_MODE_MASK BIT0 | BIT1 #define BIT1 0x02 #define PINMUX_FOR_I2C1_MODE_2 0x12

因此需要关注bank:0x103C offset:0x53 的bit[1:0] 的值是否为0x2,即是否为BIT0=0,BIT1=1,是的话说明目前I2C1_MODE_2处于使能状态

hal_pinmux.c中汇总了所有引脚的所支持的所有复用功能,相较于Tmux_Table的查询更加直观,可以直接获取到该引脚所支持的复用功能的寄存器

方法三(借助/sys/devices/virtual/sstar/msys/mux_verify节点进行确认):

| 步骤 | 说明 |

|---|---|

| A | kernel编译的时候打开OCNFIG:CONFIG_MSYS_PADMUX |

| B | 用法详见1.1 中的复用冲突的检查 |

2. 常见问题分析¶

2.1 电平控制异常¶

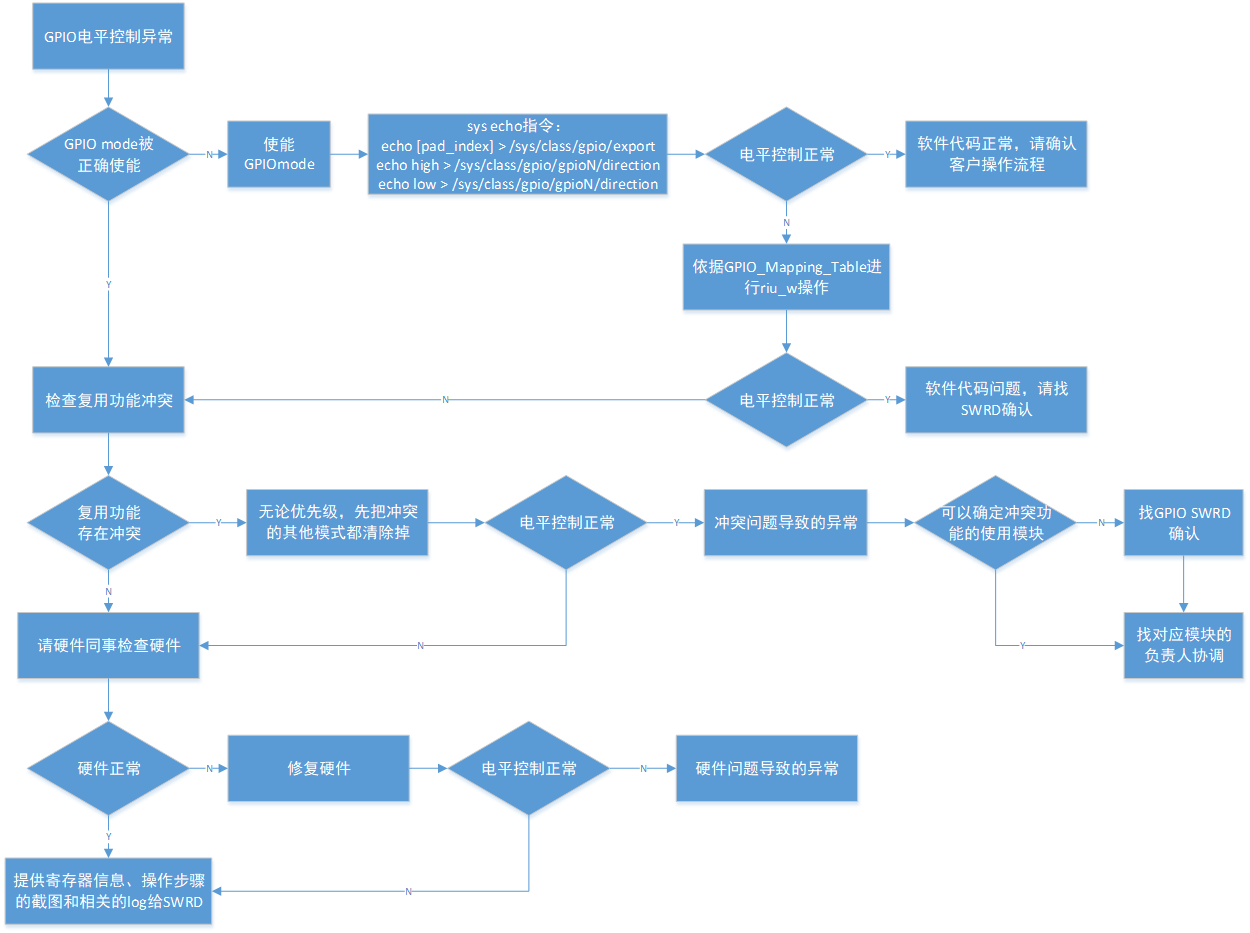

debug流程图参考如下

流程图说明: GPIO mode被正确使能的判断,请参考1.2.3 获取GPIO使能状态 复用功能存在冲突的判断,请参考1.3.2 复用功能的冲突检查 提供寄存器信息给SWRD,需要提供的寄存器包括PADTOP BANK(0x103C)和PADGPIO BANK(0x103E)

2.2 配置的复用功能未生效¶

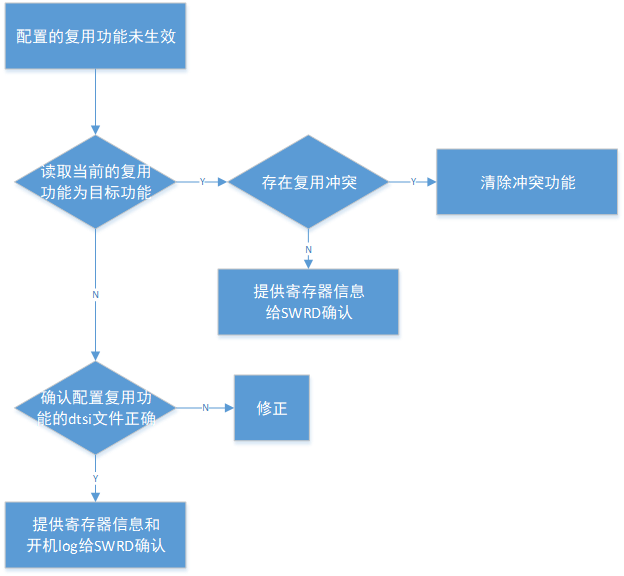

debug流程图参考如下

流程图说明: 确认配置复用功能的dtsi文件正确,可在配置文件中增加必报错的代码进行编译,如果报错表示选择的配置文件没错,没报错的话说明配错配置文件 复用功能存在冲突的判断,请参考1.3.2 复用功能的冲突检查 提供寄存器信息给SWRD,需要提供的寄存器包括PADTOP BANK(0x103C)和PADGPIO BANK(0x103E)