Panel配置参考

1. 基本介绍¶

1.1 概述¶

屏参顾名思义是屏幕使用的参数配置。本文档主要讲解点屏相关配置,屏参的含义和如何设置正确的屏参。

1.2. 关键字说明¶

-

TTL/MIPI-DSI

TTL: Transistor-Transistor Logic,接口信号为数字信号,传输并行RGB数据。

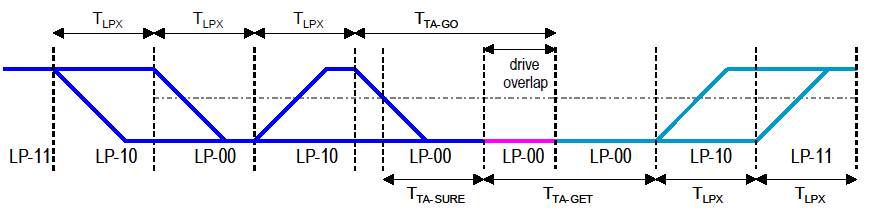

MIPI-DSI: Mobile Industry Processor Interface-Display Serial Interface,接口信号以差分信号传输,传输RGB数据,有高速HS和低速LP模式 。

2. 屏参配置文件介绍¶

2.1 屏参配置文件路径¶

project\board\$(chip)\$(boardname)\config\config_disp.json

2.2 屏参配置文件组成¶

系统启动过程中会去解析屏参配置文件,然后将不同屏参保存到系统中,给显示模块使用。显示模块会根据用户调用API的参数设定向系统获取所需屏参。 获取屏参流程请参考:MI_DISP_API

屏参配置文件组成如下图所示,mi_disp是根节点,包含三个子节点:content,屏参,PQ。

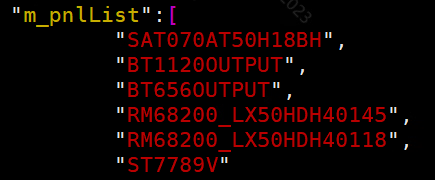

content节点是屏参名称列表的集合,包含了三个子节点:m_pnlList、m_btList、m_mipidsiList。

-

m_pnlList

m_pnlList罗列了每种接口类型的屏参名称,用户自定义屏参可放于此处,但是一种接口类型只能对应一份屏参,若存在相同类型,只会选取排在最前面的屏参。

-

m_btList/m_mipidsiList

m_btList罗列BT656多种分辨率屏参名称,m_mipidsiList罗列mipidsi多种分辨率屏参名称。

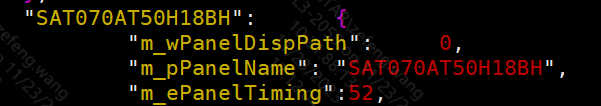

屏参由section、variable name组成:

section指的是图中屏参名称,EX:"SAT070AT50H18BH"。

variable name指的是":"左边的字段,右边是给variable name赋的值。

section是唯一的,不允许有同名,但是variable name允许。如上图,section SAT070AT50H18BH只能有一个,但是m_pPanelName可以在不同的section中。系统根据不同的section区分variable name,然后添加不同的屏参。

3. 新增屏参¶

1、新增的屏参定义的section name不允许和已有的section name重名

2、新增的屏参可以放在在m_pnlList的前面(同类panel只有第一个panel是有效的)。如果m_pnlList存在与新增屏参相同接口类型的屏参,可以将原有相同接口类型的屏参删除,也可以将新增的屏参加在原有接口屏参前面。

3、在屏参节点中添加新屏参,如下所示:

"SAT070AT50H18BH": {

"m_wPanelDispPath": 0,

"m_pPanelName": "SAT070AT50H18BH",

"m_ePanelTiming": 52,

"m_ePanelIntfType": 9,

"m_wPanelHSyncWidth": 48,

"m_wPanelHSyncBackPorch": 46,

"m_wPanelVSyncWidth": 4,

"m_wPanelVBackPorch": 23,

"m_wPanelHStart": 98,

"m_wPanelVStart": 27,

"m_wPanelWidth": 1024,

"m_wPanelHeight": 600,

"m_wPanelHTotal": 1344,

"m_wPanelVTotal": 635,

"m_wPanelDCLK": 51000000,

"m_bPanelInvDCLK": 0,

"m_bPanelInvDE": 0,

"m_bPanelInvHSync": 0,

"m_bPanelInvVSync": 0,

"m_wSpreadSpectrumFreq": 0,

"m_wSpreadSpectrumRatio": 0,

"m_ucPanelSwapChnR": 3,

"m_ucPanelSwapChnG": 2,

"m_ucPanelSwapChnB": 1,

"m_ucPanelSwapRgbML": 0

},

4. 屏参参数说明¶

4.1 公共参数¶

| 参数 | 描述 |

|---|---|

| m_pPanelName | panel name |

| m_ePanelTiming | 输出分辨率,52表示用户自定义 |

| m_ePanelIntfType | 接口类型 BT656:3 TTL:9 MIPIDSI:10 SRGB:12 |

| m_wPanelHSyncWidth | 行同步信号脉宽 |

| m_wPanelHSyncBackPorch | 行同步信号后肩 |

| m_wPanelVSyncWidth | 场同步信号脉宽 |

| m_wPanelVBackPorch | 场同步信号后肩 |

| m_wPanelHStart | m_wPanelHSyncWidth+m_wPanelHSyncBackPorch |

| m_wPanelVStart | m_wPanelVSyncWidth+m_wPanelVBackPorch |

| m_wPanelWidth | 行有效像素点数 |

| m_wPanelHeight | 场有效行数 |

| m_wPanelHTotal | m_wPanelWidth+m_wPanelHSyncWidth+m_wPanelHSyncBackPorch+HsyncFrontPorch |

| m_wPanelVTotal | m_wPanelHeight+m_wPanelVSyncWidth+m_wPanelVBackPorch+VsyncFrontPorch |

| m_wPanelDCLK | pixel clk: m_wPanelHTotal * m_wPanelVTotal * fps |

| m_bPanelInvDCLK | pixel clk极性反转 |

| m_bPanelInvDE | DE极性反转 |

| m_bPanelInvHSync | Hsync极性反转 |

| m_bPanelInvVSync | Vsync极性反转 |

| m_wSpreadSpectrumFreq | 时钟延展幅度调制(详见spreadSpectrumFreqCalculation) |

| m_wSpreadSpectrumRatio | 时钟延展频率调制(详见spreadSpectrumFreqCalculation) |

| m_ucPanelSwapChnR | Swap channel R default = 0(保持物理线路原始连接,即R通道使用硬件设计中默认对应的信号源) 1:select R(强制覆盖通道信号源,将R通道数据替换为主控输出的R通道信号) 2:select G 3:select B |

| m_ucPanelSwapChnG | Swap channel G default = 0 1:select R 2:select G 3:select B |

| m_ucPanelSwapChnB | Swap channel B default = 0 1:select R 2:select G 3:select B |

| m_ucPanelSwapRgbML | Swap RGB MSB/LSB(控制RGB数据的高低位(MSB/LSB)顺序交换) 0:disable M/L swap 1:enable M/L swap MSB:数据的最高位有效 LSB:数据的最低位有效 |

| m_ePanelRgbDataType | RGB data type or LCD data bus 0:E_MI_DISP_MHALPNL_RGB_DTYPE_RGB888, 1:E_MI_DISP_MHALPNL_RGB_DTYPE_RGB666, 2:E_MI_DISP_MHALPNL_RGB_DTYPE_RGB565, 3:E_MI_DISP_MHALPNL_RGB_DTYPE_RGB444, 4:E_MI_DISP_MHALPNL_RGB_DTYPE_RGB333, 5:E_MI_DISP_MHALPNL_RGB_DTYPE_RGB332, 6:E_MI_DISP_MHALPNL_RGB_DTYPE_BGR888, 7:E_MI_DISP_MHALPNL_RGB_DTYPE_BGR666, 8:E_MI_DISP_MHALPNL_RGB_DTYPE_BGR565, 9:E_MI_DISP_MHALPNL_RGB_DTYPE_BGR444, 10:E_MI_DISP_MHALPNL_RGB_DTYPE_BGR333, 11:E_MI_DISP_MHALPNL_RGB_DTYPE_BGR332, 12:E_MI_DISP_MHALPNL_RGB_DTYPE_YUV422_UY0VY1, 13:E_MI_DISP_MHALPNL_RGB_DTYPE_YUV422_VY0UY1, 14:E_MI_DISP_MHALPNL_RGB_DTYPE_YUV422_UY1VY0, 15:E_MI_DISP_MHALPNL_RGB_DTYPE_YUV422_VY1UY0, 16:E_MI_DISP_MHALPNL_RGB_DTYPE_YUV422_Y0UY1V, 17:E_MI_DISP_MHALPNL_RGB_DTYPE_YUV422_Y0VY1U, 18:E_MI_DISP_MHALPNL_RGB_DTYPE_YUV422_Y1UY0V, 19:E_MI_DISP_MHALPNL_RGB_DTYPE_YUV422_Y1VY0U |

| m_ePanelRgbDataSwap | RGB data swap ,对所有的数据做swap 0: disable 1: enable |

| m_wPadDrvngLvl | pin脚驱动能力调整,对接口所有的pin脚设置驱动能力档位,共有4个档位 0: 4mA 1: 8mA 2: 12mA 3: 16mA |

注:m_ePanelRgbDataType当前全部支持,12~19是BT接口可选。m_wPadDrvngLvl目前只支持0档和1档。m_ucPanelSwapRgbML是交换RGB数据传输的高低位,m_ePanelRgbDataSwap是对RGB所有数据进行交换。

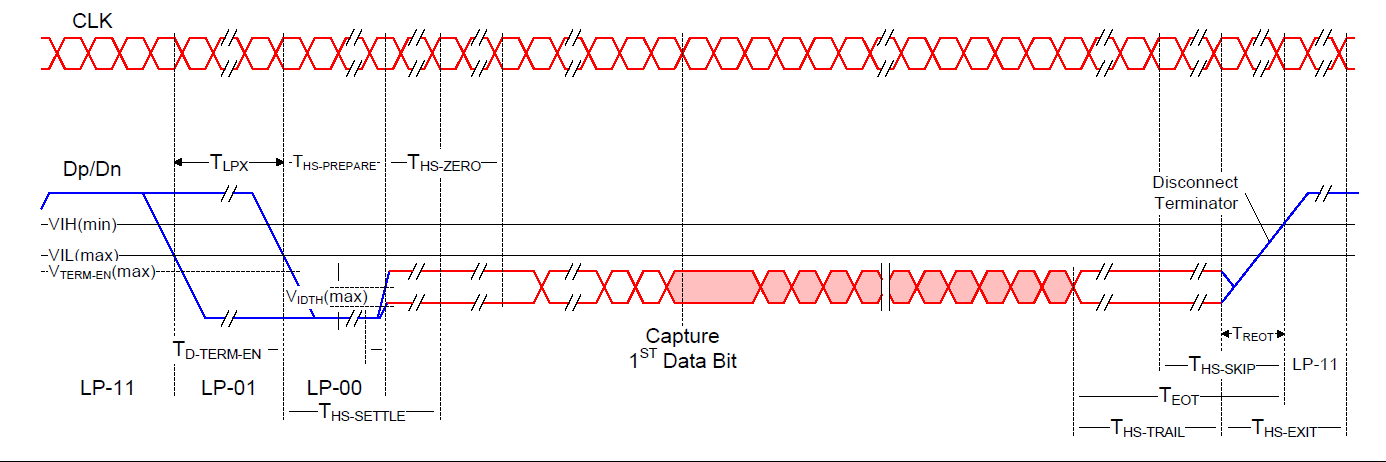

m_bPanelInvDCLK,m_bPanelInvDE,m_bPanelInvHSync,m_bPanelInvVSync正常timing示意图:

m_bPanelInvDCLK,m_bPanelInvDE,m_bPanelInvHSync,m_bPanelInvVSync开启极性反转timing示意图:

4.2 MIPIDSI接口特有参数¶

如果是MIPI panel,还需要对MIPI DSI进行配置。

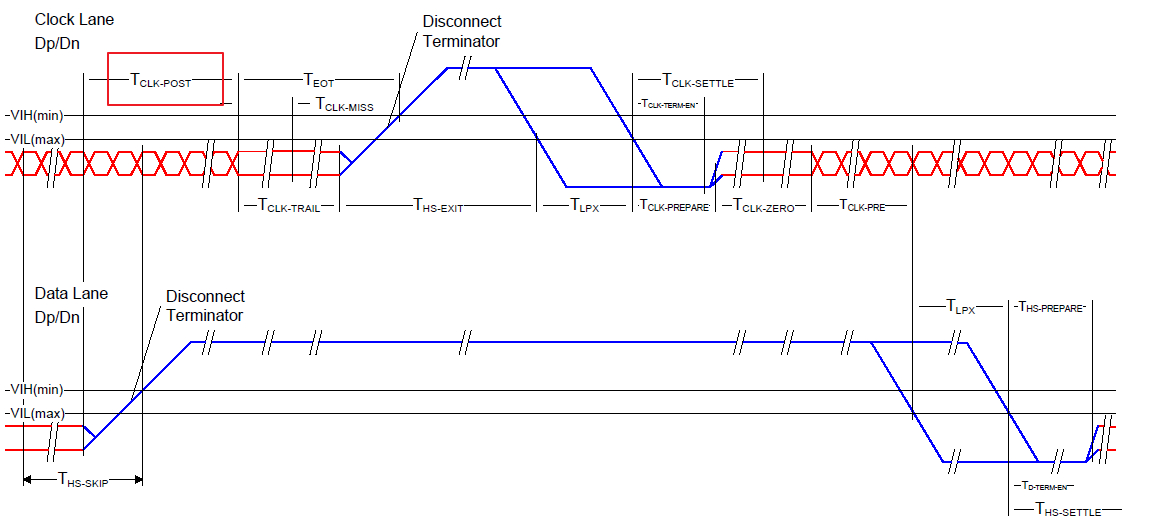

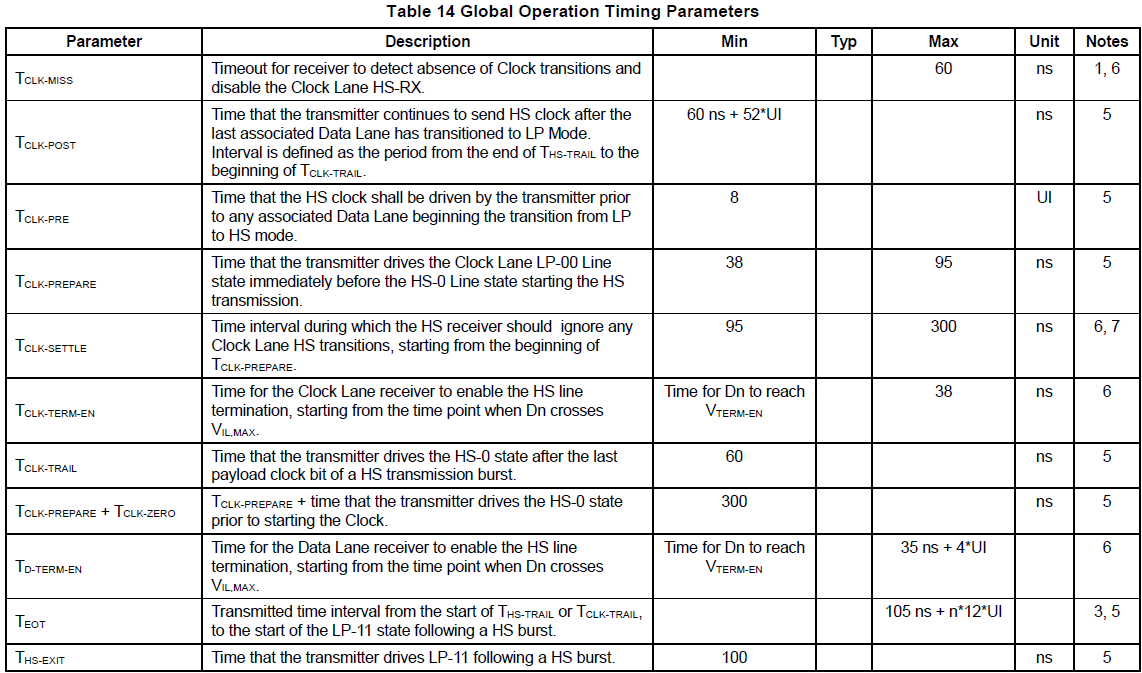

MIPI DSI参数说明:

注:如果没有特殊时序需求,目前支持自动计算m_wHsTrail、m_wHsPrpr、m_wHsZero、m_wDaHsExit、m_wClkTrail、m_wClkHsPrpr、m_wClkZero、m_wClkHsExit、m_wClkHsPost、 m_wLpx、m_wTaGet、m_wTaSure、m_wTaGo、m_wContDet。即这些参数可不填写,由代码自动计算。

注:以上dphy参数来源于MIPI_D-PHY_specification.pdf

| 参数 | 描述 |

|---|---|

| m_wHsTrail | T_{HS-TRAIL} (可参考文件配置MIPIDSIParamCalculation) |

| m_wHsPrpr | T_{HS-PREPARE} (可参考文件配置MIPIDSIParamCalculation) |

| m_wHsZero | T_{HS-ZERO} (可参考文件配置MIPIDSIParamCalculation) |

| m_wDaHsExit | T_{HS-EXIT} (可参考文件配置MIPIDSIParamCalculation) |

| 参数 | 描述 |

|---|---|

| m_wClkTrail | T_{CLK-TRAIL} (可参考文件配置MIPIDSIParamCalculation) |

| m_wClkHsPrpr | T_{CLK-PREPARE} (可参考文件配置MIPIDSIParamCalculation) |

| m_wClkZero | T_{CLK-ZERO} (可参考文件配置MIPIDSIParamCalculation) |

| m_wClkHsExit | T_{HS-EXIT} (可参考文件配置MIPIDSIParamCalculation) |

| m_wClkHsPost | T_{CLK-POST} (可参考文件配置MIPIDSIParamCalculation) |

| 参数 | 描述 |

|---|---|

| m_wLpx | T_{LPX} (可参考文件配置MIPIDSIParamCalculation) |

| m_wTaGet | T_{TA-GET} (可参考文件配置MIPIDSIParamCalculation) |

| m_wTaSure | T_{TA-SURE} (可参考文件配置MIPIDSIParamCalculation) |

| m_wTaGo | T_{TA-GO} (可参考文件配置MIPIDSIParamCalculation) |

| m_wContDet | contention detection, default 0(可参考文件配置MIPIDSIParamCalculation) |

| m_wBllp | blanking or low power interval, default 0 |

| m_wFps | frame per second, follow panel spec |

| m_eLaneNum | data lane number, 1 ~ 4 |

| m_eFormat | data output format 0:RGB565 1:RGB566 2:LOOSELY_RGB666 3:RGB888 |

| m_eCtrlMode | 0:CMD_MODE 1:SYNC_PULSE 2:SYNC_EVENT 3:BURST_MODE |

| m_wDataClkSkew | defult: 7 |

| m_ucPolCh0 | Channel 0 polarity 0:default 1:positive |

| m_ucPolCh1 | Channel 1 polarity 0:default 1:positive |

| m_ucPolCh2 | Channel 2 polarity 0:default 1:positive |

| m_ucPolCh3 | Channel 3 polarity 0:default 1:positive |

| m_ucPolCh4 | Channel 4 polarity 0:default 1:positive |

| m_ucClkLane | clk lane selection 0:select chn0 1:select chn1 2:select chn2 3:select chn3 4:select chn4 |

| m_ucDataLane0 | data lane0 selection 0:select chn0 1:select chn1 2:select chn2 3:select chn3 4:select chn4 |

| m_ucDataLane1 | data lane1 selection 0:select chn0 1:select chn1 2:select chn2 3:select chn3 4:select chn4 |

| m_ucDataLane2 | data lane2 selection 0:select chn0 1:select chn1 2:select chn2 3:select chn3 4:select chn4 |

| m_ucDataLane3 | data lane3 selection 0:select chn0 1:select chn1 2:select chn2 3:select chn3 4:select chn4 |

| m_pCmdBuff | MIPI panel cmd buffer, follow panel spec |

| m_pDeinitCmd | MIPI panel deinit cmd buffer, follow panel spec, 内容格式与m_pCmdBuff相同,如不需要可删除该参数 |

m_pCmdBuff是panel初始化cmd,该部分是各panel厂商参照协议标注自定义的,因此该参数设定内容一般找panel厂商提供。该参数的设定内容格式如下所示,以十六进制填写。

"m_pCmdBuff":[

"cmd1","data_num","data[0]","data[1]",...,"data[num-1]",

...,

"cmdN","data_num","data[0]","data[1]",...,"data[num-1]",

"0xFF","0xFF" //结束符

]

| 参数 | 描述 |

|---|---|

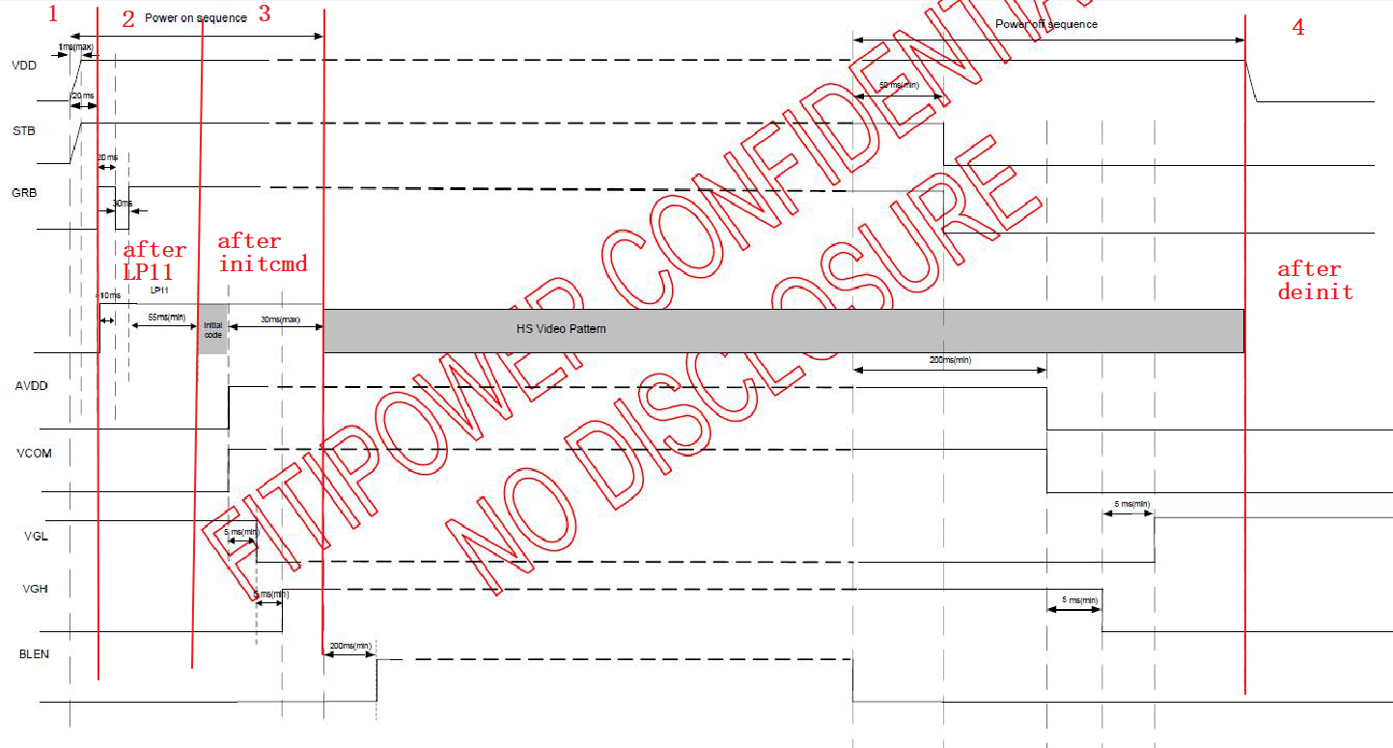

| m_pAfterLP11 | LP11之后,power on时序控制,如不需要可删除该参数 |

| m_pAfterInit | mipidsi init cmd发送完成后,power on时序控制,如不需要可删除该参数 |

| m_pAfterDeinitCmd | mipidsi deinit cmd发送完成后,power off 时序控制,如不需要可删除该参数 |

m_pAfterLP11、m_pAfterInit、m_pAfterDeinitCmd 用于控制屏幕的上下电时序,内容格式如下所示。pin_idx后面必须跟上level和delay_ms,以十进制填写。

"m_pAfterLP11":[

"pin_idx","level","delay_ms",

"pin_idx","level","delay_ms",

...,

"pin_idx","level","delay_ms"

]

示例:seq-after-lp11:拉高gpio_179并延时10ms -> 拉低gpio_179并延时10ms -> 拉高gpio_179并延时10ms。

seq-after-lp11 = <179 1 10 179 0 10 179 1 10>; seq-after-initmd = <179 1 10 179 0 10 179 1 10>; seq-after-deinitcmd = <179 1 10 179 0 10 179 1 10>;

¶

¶

5. 配置正确的屏参¶

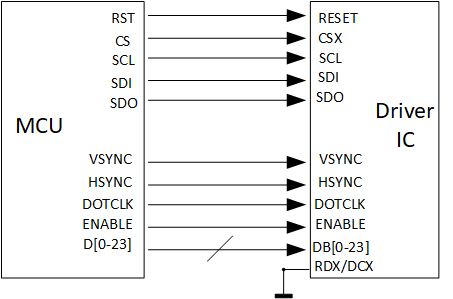

配置正确的屏参除了可以参考上述列表中的附件表格,还需要根据屏幕规格书或者协议规范调整对应的参数。

5.1 屏幕规格书¶

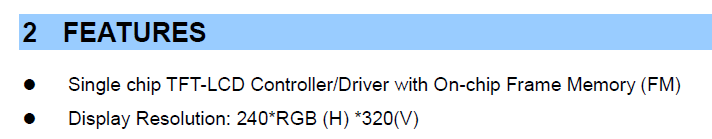

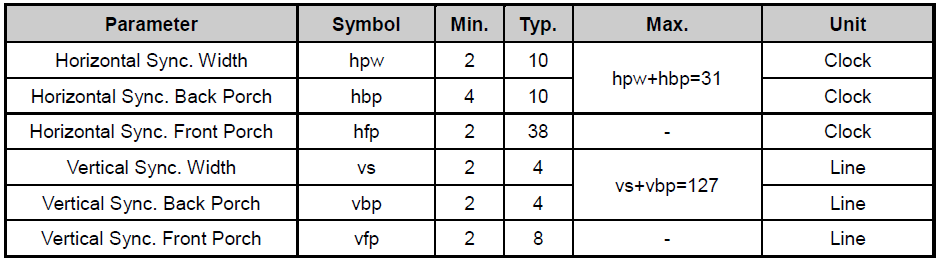

大部分屏芯片的规格书可以找到Timing相关部分,如下图所示。如果找不到,可以找厂家询问。

| 参数 | 描述 |

|---|---|

| m_wPanelVSyncWidth | Horizontal Sync. Width |

| m_wPanelHSyncBackPorch | Horizontal Sync. Back Porch |

| m_wPanelVSyncWidth | Vertical Sync. Width |

| m_wPanelVBackPorch | Vertical Sync. Back Porch |

| m_wPanelHStart | m_wPanelHSyncWidth+m_wPanelHSyncBackPorch |

| m_wPanelVStart | m_wPanelVSyncWidth+m_wPanelVBackPorch |

| m_wPanelWidth | 240(H) |

| m_wPanelHeight | 320(V) |

| m_wPanelHTotal | m_wPanelHStart+m_wPanelWidth + hfp |

| m_wPanelVTotal | m_wPanelVStart+m_wPanelHeight + vfp |

5.2 协议规范¶

如果是MIPI panel,还需要根据MIPI spec配置MIPI dphy相关参数。

UI的计算方法: H_Total = m_wPanelHTotal V_Total = m_wPanelVTotal BitsPerPixel=24(RGB888)/18(RGB666)/16(RGB565) Bitrate = H_Total * V_Total * FPS * BitsPerPixel / lane number UI = 1/Bitrate

比如表格中HS-PREPARE的要求是大于(40ns + 4 * UI)并且小于(85ns + 6 * UI),那么对应MIPI dphy timing中的参数

(40ns + 4 * UI) / 8 * UI < m_wHsTrail < (85ns + 6 * UI) / 8 * UI

其他MIPI dphy timing中参数计算方法同上。

hpw、hbp、hfp需满足下列公式

data_init_cycle = HsExit + Lpx + HsPrpr + HsZero HFP_WC = HFP * BPP – 12 – data_init_cycle * lane_num HBP_WC = HBP * BPP – 10 HSA_WC = HPW * BPP – 10 HFP_WC/HBP_WC/HSA_WC need > 0

上述参数计算都可参考文件 MIPIDSIParamCalculation。

6. TTL配置¶

6.1 基本概念¶

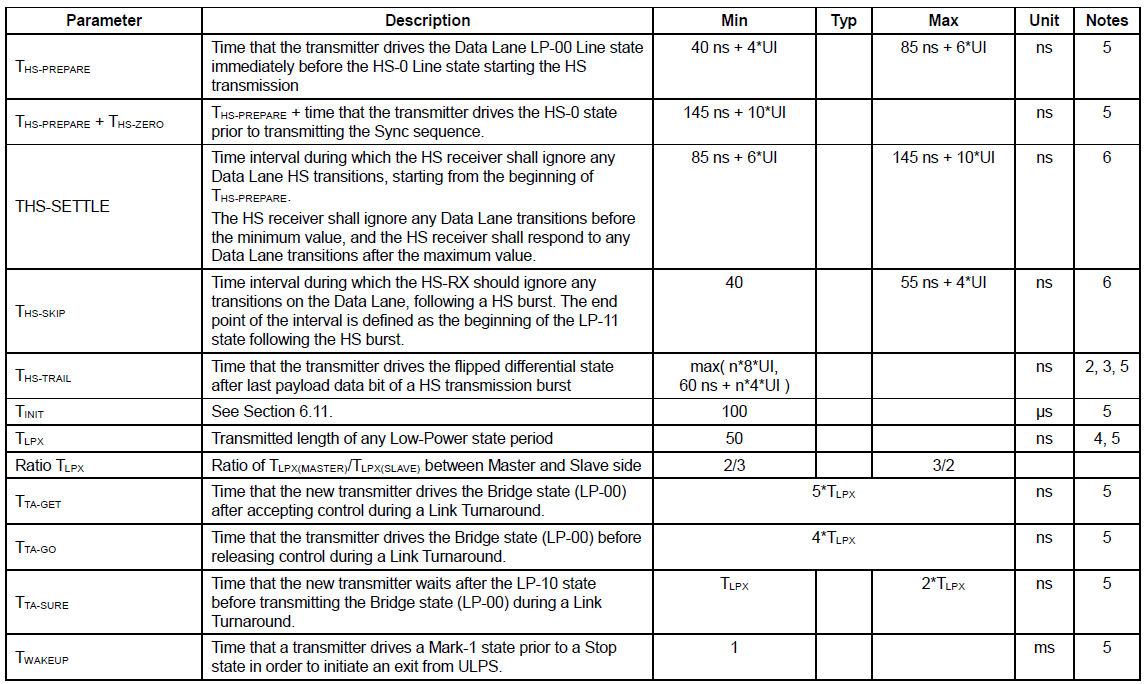

Parallel RGB Interface有两种,DE mode和HV mode,当使能DE的时候,会使用VSYNC、HSYNC、DOTCLK、DE、D[0-23]这些pin,当使能HV mode的时候,会使用VSYNC、HSYNC、DOTCLK、D[0-23]。现在程序默认使用DE mode,相关参数请按照DE mode配置。

一些panel driver IC需要对其初始化,即对其内部register进行设定,一般会通过SPI或者IIC接口来通信,初始化需要的cmd和data是由屏厂提供,发送时的数据格式需要参考panel datasheet。

Parallel RGB Interface的panel通过HSYNC、VSYNC、DOTCLK、DE作为同步信号,RGB data只在timing的有效区间显示,blanking区间是不可见区域。

6.2 padmux¶

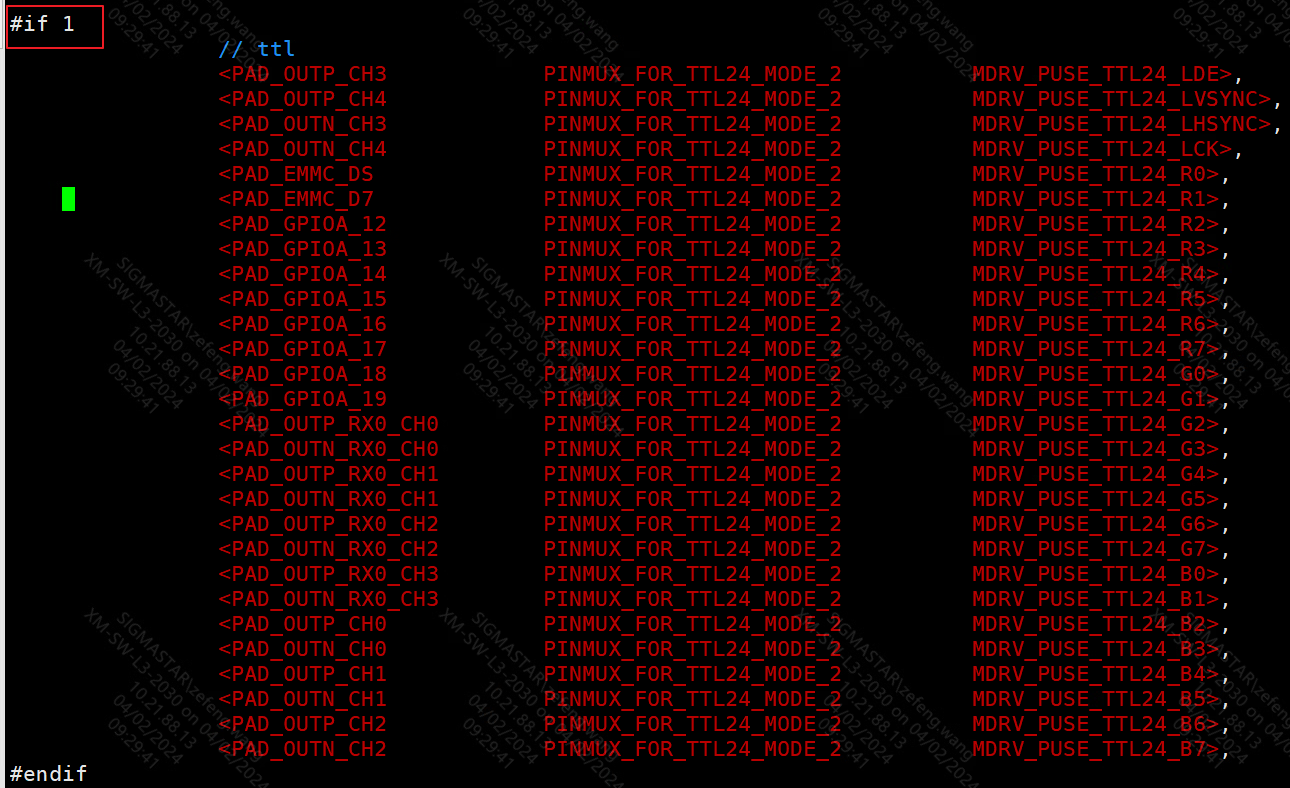

kernel/arch/arm64/boot/dts/sstar/$(boardname)-padmux.dtsi

可如下配置,将#if 0 更改为 #if 1

6.3 屏参配置¶

新屏参设置请参考第2章,屏参内容设置请参考4、5章。

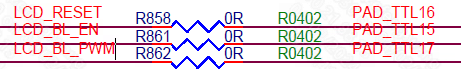

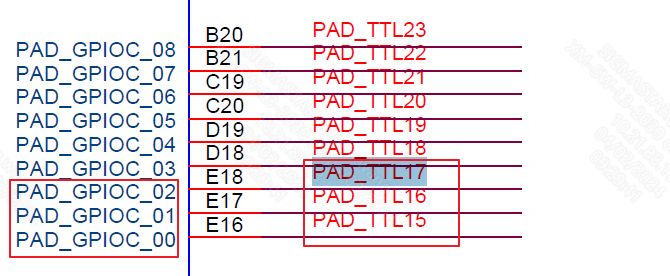

6.4 背光¶

如果需要背光控制,在原理先找出对应Pin脚和芯片对应的pad,通过控制上述pin脚来达到控制背光的效果

7.MIPIDSI配置¶

7.1 MIPIDSI规格¶

- 1-4 data lanes, 1 clock lane

- Level:

- LP: 0~1.2V

- HS: 100~300mV

- HS: 80Mbps ~ 2.5Gbps/lane

- Pixel format:

- 16 bpp (5,6,5 RGB) each pixel using two bytes

- 18 bpp (6,6,6 RGB) packed

- 18 bpp (6, 6, 6 RGB) loosely packed into three bytes

- 24 bpp (8, 8, 8 RGB), each pixel using three bytes

- video mode: BURST_MODE/SYNC_EVENT/SYNC_PULSE

- data chn swap

- data/clk chn P/N swap

- max resolution 2560x1440@60

7.2 padmux¶

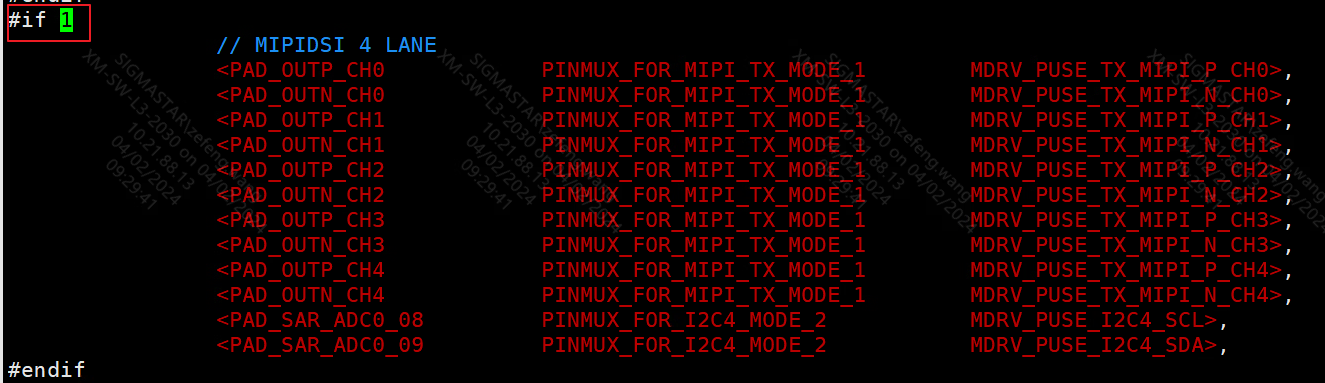

kernel/arch/arm64/boot/dts/sstar/$(boardname)-padmux.dtsi

可如下配置,将#if 0 更改为 #if 1

7.3 屏参配置¶

新屏参设置请参考第2章,屏参内容设置请参考4、5章。

7.4 背光¶

背光控制与TTL一致。