TrustZone概述¶

REVISION HISTORY¶

| Revision No. | Description |

Date |

|---|---|---|

| 1.0 | 05/22/2023 |

1. SGS TRUSTZONE介绍¶

1.1. 概述¶

ARM TrustZone是一套硬件层级的强制隔离技术,将处理器的执行状态分为两个区域:

-

secure world:用于运行可信软件;

-

non-secure world:用于运行不可信软件。

将设备硬件和内存等资源也进行切分:

-

CPU跑在non-secure world时,只能访问non-secure 资源;

-

CPU跑在secure world可以访问secure资源和non-secure资源。

ARM TrustZone旨在阻挡消费者通过操作系统或者应用程序漏洞进行攻击,读写硬件和软件资源。SGS Chip遵循ARM TrustZone的技术及规范来实现系统安全性的功能。

1.2. SGS TrustZone硬件¶

官方文档《trustzone_securit_whitepaper.pdf》提供更详细的trustzone硬件架构介绍:https://developer.arm.com/documentation/PRD29-GENC-009492/latest/

SGS TrustZone主要的硬件模块涉及CPU,secure interrupt group,TZIMI,TZEMI,TZSP。

1.2.1 CPU Security¶

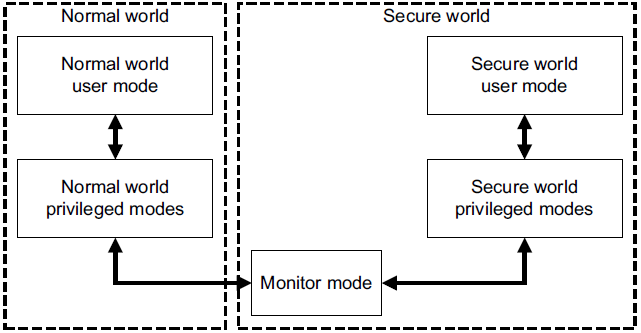

图1 S/NS-wrold

一个实体的CPU core被分成两个虚拟的CPU core: 一个为secure core,另一个为non-secure core。secure及non-secure core之间相互切换过程,CPU需要先进入monitor mode处理器模式。ARM提供了smc(Secure Monitor Call)指令,这个指令执行之后, CPU会切换到monitor模式。处在secure world的CPU可以通过SMC 指令切换到Secure Monitor模式,SMC的软中断具体处理函数在BL31实现,SMC中断处理函数会根据发送指令是属于安全侧请求还是非安全侧的请求来控制是将cortex切换到secure world态还是non-secure world态。secure world切换到non-secure world过程亦然。

Non-secure world -> secure world两种情况:

-

Non-secure world执行代码时,调用SMC

-

Non-secure world执行代码时,发生group0中的中断

Secure world -> Non-secure world两种情况:

-

Secure world执行代码时,调用SMC

-

Secure world执行代码时,发生group1中的中断

1.2.2 Interrupt Security¶

TrustZone设计下,所有interrupts被分成两种group:

-

Group 0

-

Group 0 interrupt永远为secure

-

可以以FIQ或IRQ形式发出

-

通常是发给OPTEE OS的interrupt

-

-

Group 1

-

Group 1 interrupt永远为non-secure

-

永远以FIQ形式发出

-

通常是发给linux os处理的interrupt

SGS Chip通过软件预设每个interrupt指定为两个群组中之一,来保证secure interrupt只能被trusted os处理。

-

1.2.3 DRAM Security¶

SGS chip里基本上所有CPU和IP都可以访问DDR。整片DDR最多可以被划分成17个region。DRAM的安全访问由TZEMI来保证。TZEMI从硬件设计上将所有能访问DDR的IP划分S/NS属性,而每个DDR region也被TZEMI从硬件设计上划分S/NS属性。当CPU和IP(Master)访问DRAM region(Slave)时,TZEMI会判断安全属性来决定此次访问是否为合法。

1.2.4 SRAM Security¶

SGS chip里能访问SRAM的master包含:MCU/VENC0/AESDMA/SD30/BDMA/SDIO/FCIE。整片SRAM最多可以被划分成2个region。SRAM的安全访问由TZIMI来保证。TZIMI从硬件设计上将IMI client划分S/NS属性,而每个SRAM region也被TZIMI从硬件设计上划分S/NS属性。当IMI client(Master)访问IMI region(Slave)时,TZIMI会判断安全属性来决定此次访问是否为合法。

1.2.5 IP Security¶

SGS chip里能访问IP的master包含:CPU/CMDQ0/CMDQ1/VENC-RISVC/ISP0-CMDQ/debug port,而所有被访问的IP划分在不同的RIU bank。IP的安全访问由TZSP来保证。TZSP从硬件设计上将RIU master IP划分S/NS属性,而每个RIU bank也被TZSP从硬件设计上划分S/NS属性属性。当RIU master IP访问RIU bank(Slave)时,TZSP会判断安全属性来决定此次访问是否为合法。

1.3. OP-TEE软件架构¶

OP-TEE(Open Portable Trusted Execution Environment)是一个开源的可移植的可信执行环境。基于TrustZone技术的硬件隔离和安全监控机制,TEE运行在trustzone的secure Domain中,与普通操作系统(如linux/rtk/freertos)运行在trustzone的no-secure Domin相隔离。

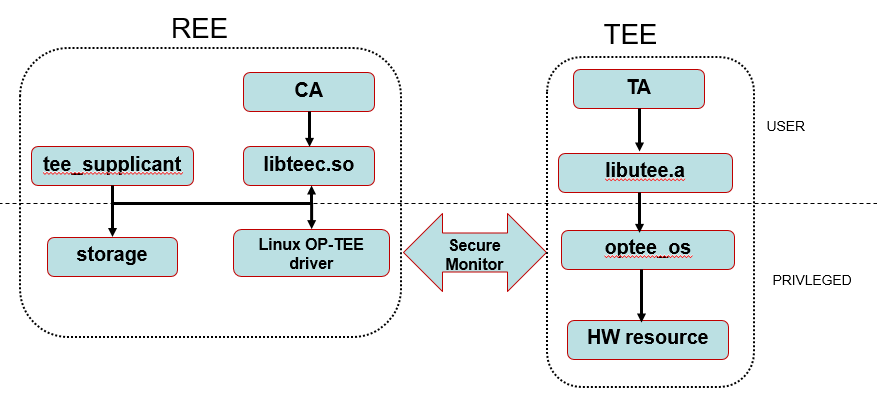

图2 软件架构

运行在SGS Chip上的软件系统可以被分为TEE及REE两个部分。

REE(Rich Execution Environment):指的是普通的操作系统执行环境,代指linux。

TEE(Trusted Execution Environment):指的是可信任执行环境,代指OP-TEE。

TA(trust applicant):代指在OP-TEE运行的应用。

CA(client applicant):代指在linux运行的应用。

libteec库:是OP-TEE提供给用户在linux userspace层面调用的接口实现。

tee_supplicant:启动后作为Linux中的一个后台程序运行,通过类似于C/S的方式为OP-TEE提供对REE端(linux)文件系统的操作。tee_supplicant的主要作用是使OP-TEE能够通过tee_supplicant来访问REE端(linux)文件系统中的资源,例如加载存放在文件系统中的TA镜像到TEE中。

OP-TEE驱动:主要作用是REE与TEE端进行数据交互的桥梁作用。tee_supplicant和libteec调用接口首先通过系统调用陷入到kernel space的OP-TEE驱动get_invoke_func函数代码里,最终会通过发出smc切换到monitor,将调用接口时传下来的数据发送给secure world来进行处理。

libutee库:在OP-TEE中userspace的接口一般定义成utee_xxx_xxx的形式,这些由GP(Gloable Platform)统一定义的接口一般在libutee.a库里实现,而其对应的system call则为syscall_xxx_xxx。

HW resource:目前SGS平台软件预设受保护的资源如下:

-

MIIC0

-

OTP ctrl

-

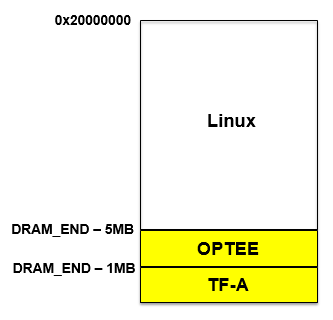

TF-A及tee os内存(以下标黄色DDR段)

图3 MIU layout

更详细的optee软件架构介绍需要阅读官方网站:https://optee.readthedocs.io/en/latest/index.html

1.4. SGS TrustZone启动流程¶

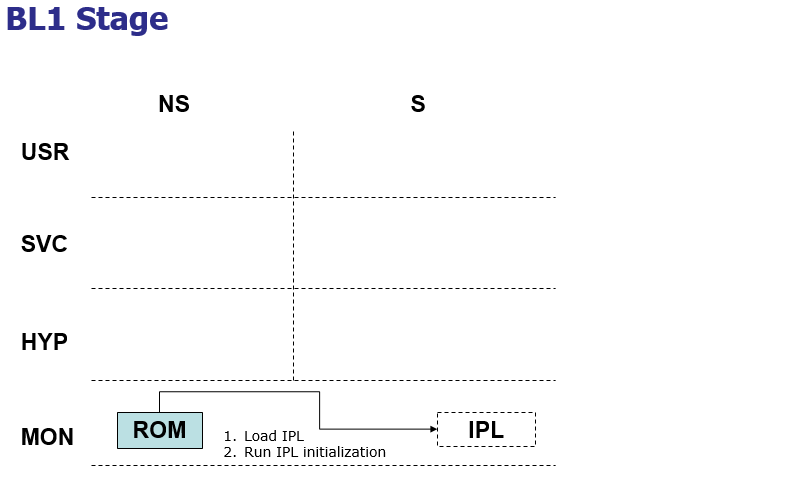

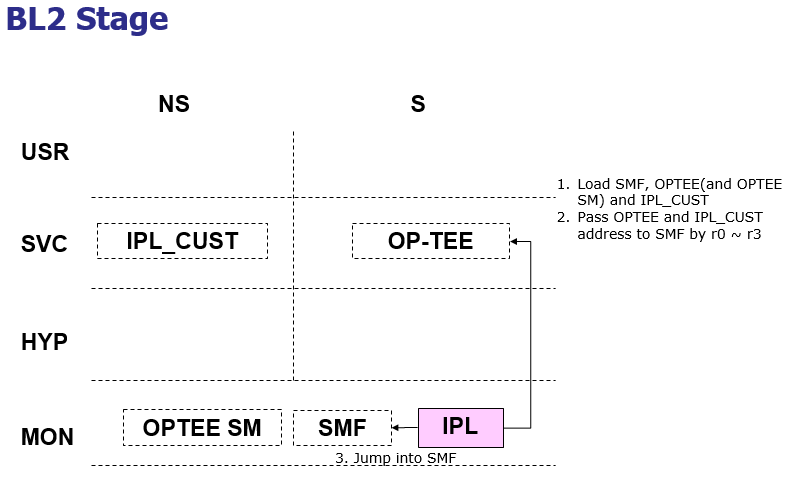

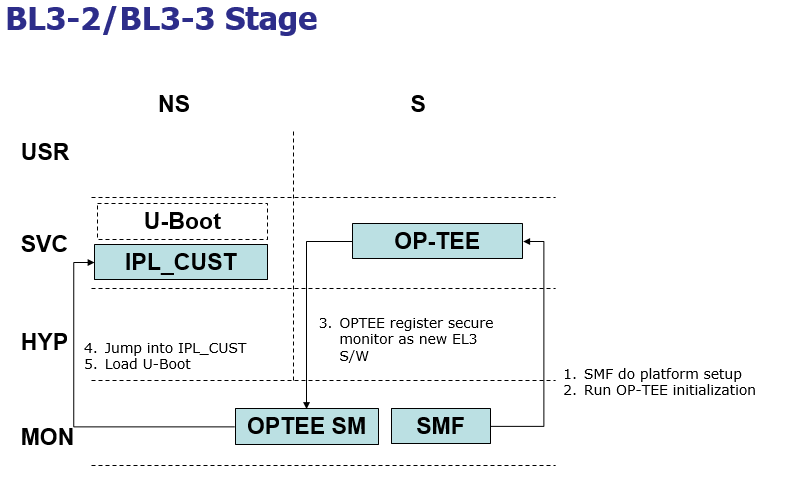

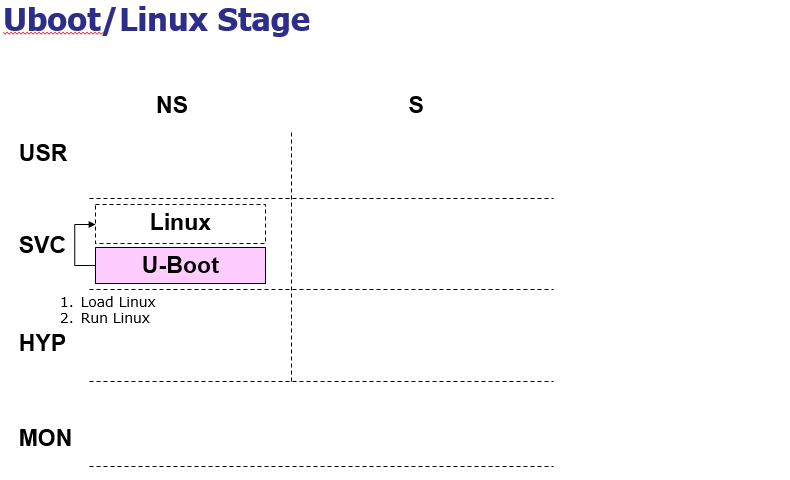

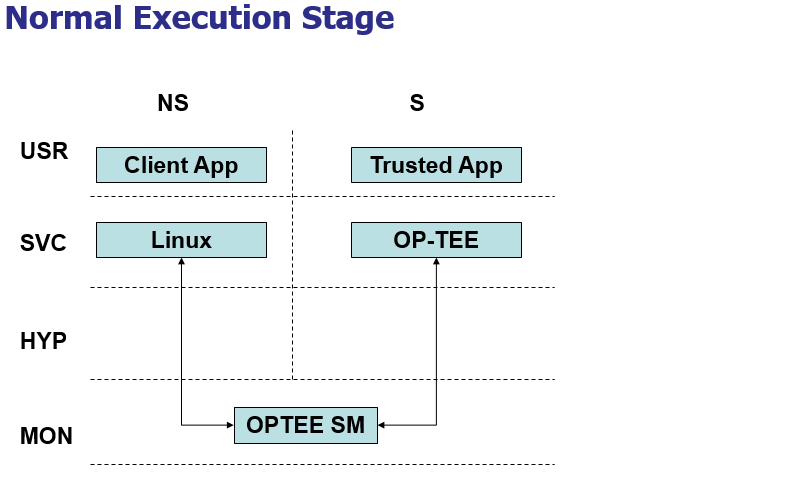

根据ARM架构定义,整个系统分成四种运行等级,分别为:USR,SVC,HYP,MON。SGS平台对应软件启动流程为:

图4 启动流程-1

图5 启动流程-2

图6 启动流程-3

图7 启动流程-4

图8 启动流程-5