PSPI使用参考¶

REVISION HISTORY¶

| Revision No. | Description |

Date |

|---|---|---|

| 1.0 | 04/02/2025 | |

| 1.1 | 11/24/2025 |

1. 概述¶

Serial Peripheral Interface (串行外围设备接口),简称SPI, 是 Motorola 公司推出的一种高速同步串行接口技术,主要应用在EEPROM,Flash,实时时钟(RTC),数模转换器(ADC),数字信号处理器(DSP) 等设备。

本文主要介绍Sigmaster PSPI使用。

2. 关键字说明¶

-

D0:Master output slave input 主机输出,从机输入(数据来自主机)

-

D1:Master input slave output 主机输入,从机输出(数据来自从机)

-

SCLK / SCK : Serial Clock 串行时钟信号,由主机产生发送给从机

-

CS / SS:Slave Select 片选信号,由主机发送,以控制与哪个从机通信,通常是低电平有效信号

-

CPOL / CKP:时钟极性,表示时钟的默认状态下的电平高低状态

-

CPHA / CKE:时钟相位,表示采集数据时是在时钟信号的具体相位

-

SPI Mode :SPI的时钟极性和相位的配置可以输出4种SPI模式

SPI Mode CPOL CPHA 0 [00] 0 0 1 [01] 0 1 2 [10] 1 0 3 [11] 1 1

3. 功能描述¶

-

PSPI(Programmable SPI)支持master和slave模式。

-

PSPI不支持全双工,只支持半双工,支持DMA模式。FIFO模式只有作为master支持。

-

master和slave都支持4线通讯(MISO + MOSI + D0 + D1)、3线master通讯(MOSI + SCLK + D0),3线slave通讯(MOSI + SCLK + D1)

-

16 Byte读写缓冲区(FIFO mode),字传输3bit到32bit可配置位宽度;DMA字宽8bit。

-

硬件预设的片选设定,PSPI支持硬件片选2个。

-

Source Clock:12M、24M、pll_source/2M、pll_source/4M(pll_source默认200M,可调为192M),Slave通讯频率为Source Clock ¼。而PSPI Master通讯频率的可选档位则是每种Source Clock的分频的,分频系数为1~255。公式:speed = src_clk/(2*div + 2)。PSPI Slave实际的通讯频率会选择不小于目标频率的档位;PSPI Master实际的通讯频率会选择最接近目标频率但小于目标频率的档位,以Source Clock为12Mhz举例,部分分频如下表,如果目标频率是800000HZ,那么实际通讯频率为750000HZ。

div SPI Clock Rate formula 1 3000000 Source Clock / 4 2 2000000 Source Clock / 6 3 1500000 Source Clock / 8 4 1200000 Source Clock / 10 5 1000000 Source Clock / 12 6 857142 Source Clock / 14 7 750000 Source Clock / 16 8 666666 Source Clock / 16 -

支持PSPI数量:

chipname bank pspi number iford 0x19 1

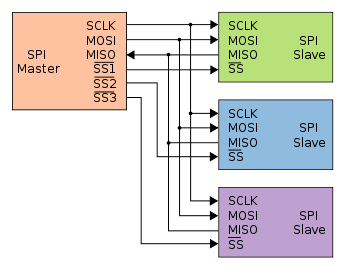

4. 硬件连接¶

5. Kernel用法介绍¶

5.1. Kernel Config配置¶

kernel使用PSPI,需要配置:

CONFIG_SPI=y //SPI核心,必选

CONFIG_SSTAR_PSPI=y //PSPI控制器驱动,必选

CONFIG_SPI_SPIDEV=y //spidev设备驱动,可选

CONFIG_SPI_SLAVE=y //开启slave模式

menuconfig选择的配置如下:

Device drivers->

[*] SPI support->

<*> User mode SPI device driver support

[*] SPI slave protocol handlers

Device drivers->

[*] SStar SoC platform drivers->

<*> SStar PSPI driver

5.2. Dts配置¶

pspi: spi@1F003200 {

compatible = "sstar,pspi";

reg = <0x1F003200 0x200>;

#address-cells = <1>;

#size-cells = <0>;

interrupts = <GIC_SPI INT_IRQ_PSPI02HOST IRQ_TYPE_LEVEL_HIGH>;

clocks = <&CLK_pm_pspi0>;

#ifdef CONFIG_SPI_SLAVE

pspi-slave;

#endif

dma-enable;

group = <1>;

cs-num = <1>;

status = "okay";

#ifdef CONFIG_SPI_SLAVE

slave@0 {

compatible = "ge,achc";

reg = <0>;

};

#else

spidev1@0 {

compatible = "ge,achc";

reg = <0>;

};

#endif

};

PSPI驱动中支持配置的属性如下:

| 属性 | 描述 | 备注 |

|---|---|---|

| compatible | 用于匹配驱动进行驱动注册,需与代码中一致 | 禁止修改 |

| reg | 用于指定SPI寄存器bank的地址 | 禁止修改 |

| interrupts | 用于指定使用的硬件中断号及属性 | 禁止修改 |

| clocks | 用于指定使用的时钟源 | 禁止修改 |

| pspi-slave | 用于指定是否为slave模式 | 可根据需要修改 |

| group | 用于指定SPI外设编号序列号 | 不需要修改 |

| dma-enable | 用于指定是否使能DMA模式 | 可根据需要修改 |

| cs-num | 用于指定Engine自带的cs pad的数量 | 可根据需要修改 |

| status | 用于选择是否使能SPI master驱动 | 可根据需要修改 |

| slave@0 | 用于注册spi设备,用户空间透出节点/dev/spidev*.*,reg表示选择哪个片选 | 最多只能有一个 |

| spidev1@0 | 用于注册spi设备,用户空间透出节点/dev/spidev*.*,reg表示选择哪个片选 | 可根据需求增删 |

5.2.1. pspi-slave¶

PSPI支持Master和Slave模式,如果要作为Slave,需要内核配置Slave外,还需要将DTS配置pspi-slave。

5.2.2. dma mode¶

PSPI Master支持两种基本通信模式:buffer mode和dma mode。当SPI Master处于buffer mode工作模式时,需要软件参与发送buffer和接收buffer的操作,所以波形会受到软件调度的影响,在每次发送的之间会产生一定间隔。

当PSPI Master和Slave处于dma mode工作模式时,驱动只需将需要发送的数据的地址和接收的数据需要存放的地址设置到SPI Master DMA相关的寄存器中后,SPI Master会自动连续发送和接收数据,此过程不需要软件参与。因此当PSPI工作在dma mode时,SPI的波形连续性较好。

5.2.3. cs-num¶

最大值为硬件预设的cs数量,如cs-num = 1,就只使用一个硬件cs。

5.2.4. slave¶

PSPI Slave模式下,使用drivers/spi/spidev.c驱动时必须配置,即宏CONFIG_SPI_SPIDEV,完成spidev设备注册。注册完成用户态会出现/dev/spidev*.*字符设备。只能配置一个。

5.2.5. spidev¶

PSPI Master模式下,使用drivers/spi/spidev.c驱动时必须配置,即宏CONFIG_SPI_SPIDEV,完成spidev设备注册。注册完成用户态会出现/dev/spidev*.*字符设备。可根据cs个数增删节点个数。

5.3. PADMUX配置¶

PSPI在Linux环境下的padmux配置,只需要根据选择的引脚加入在对应的padmux.dtsi中,如下配置PSPI0的mode1引脚:

<PAD_PM_PSPI0_DI PINMUX_FOR_PM_PSPI0_MODE_1 MDRV_PUSE_PSPI0_MISO0>,

<PAD_PM_PSPI0_DO PINMUX_FOR_PM_PSPI0_MODE_1 MDRV_PUSE_PSPI0_MOSI0>,

<PAD_PM_PSPI0_CK PINMUX_FOR_PM_PSPI0_MODE_1 MDRV_PUSE_PSPI0_CLK>,

<PAD_PM_PSPI0_CZ PINMUX_FOR_PM_PSPI0_MODE_1 MDRV_PUSE_PSPI0_CS>,

第一列为引脚索引号,可以在drivers/sstar/include/{chipname}/gpio.h中查到;

第二列为模式定义,在drivers/sstar/gpio/{chipname}/hal_pinmux.c中m_hal_gpio_st_padmux_entry数组里,罗列了所有引脚的复用关系,查询该引脚支持哪些复用功能可以查询该数组;

第三列为引脚及搭配模式的索引名称,可在drivers/sstar/include/drv_puse.h里查询,请配置为PSPI相关的puse。

6. 测试用例说明¶

6.1 Linux参考用例¶

-

drivers/sstar/pspi/ut/pspi_ut.c

示例:作为master,测试外挂nandflash读写

./pspi_ut -D /dev/spidev1.0 -s 6000000

7. PSPI限制¶

- PSPI DMA模式从外部单次读取的数据超过512Byte时,PSPI的最大工作频率 要小于等于 ½ PM IMI的频率(DMA buffer在PM IMI)。

8. FAQ¶

-

PSPI slave只能连接到SPI Master。

-

Slave和Master 4根线的电压要一样,如都是1V8,要共地。

-

如果抓到的数据有点异常,可以加大引脚驱动能力。

-

Master与Slave收发数据大小一致。否则可能会遇到Slave驱动卡住现象。

-

注意Slave的clock不大于Master的clock。

-

PSPI dma模式的buffer驱动配置了4KB,如果需要改大/改小,在kernel/driver/sstar/pspi/drv_pspi.c中修改

PSPI_DMA_ALLOC_SIZE的值。 如果使用spidev.c,同时需要修改/kenrel/drivers/spi/spidev.c中bufsiz的值。在spidev.c中,bufsiz的默认值为4096,即4kB。 -

由于SPI通信的时钟是Master打出的,所以应该等Slave准备就绪,再执行Master输出Clock操作。

-

确认引脚连接,padmux配置是否正确,注意Clock引脚的PUSE配置,如果PSUE配置错了,可能导致CPOL=1时波形异常,通信失败。